S3C2410A LCD CONTROLLER

15-29

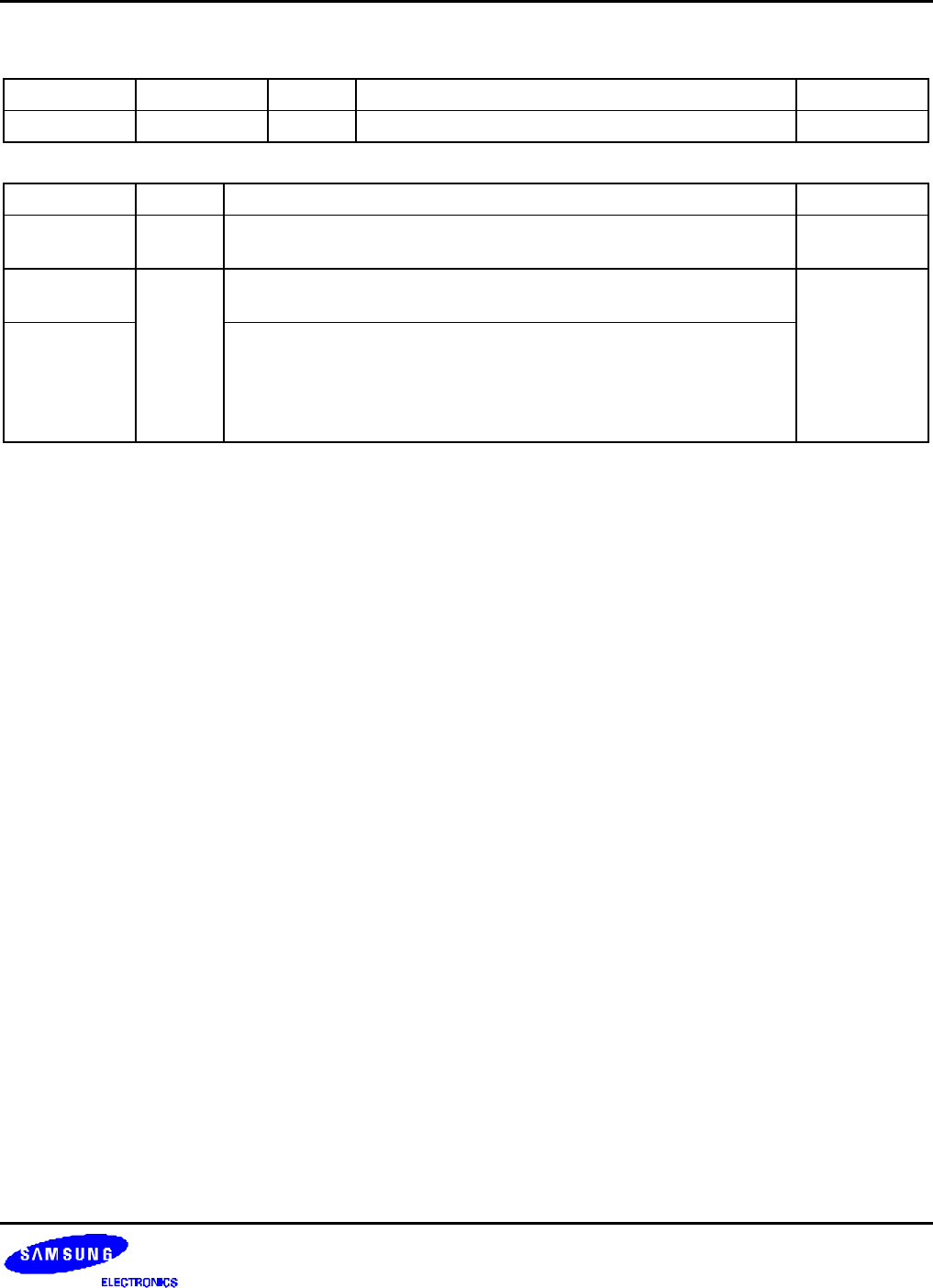

LCD Control 4 Register

Register Address R/W Description Reset Value

LCDCON4 0X4D00000C R/W LCD control 4 register 0x00000000

LCDCON4 Bit Description Initial state

MVAL [15:8] STN: These bit define the rate at which the VM signal will toggle if the

MMODE bit is set to logic '1'.

0X00

HSPW(TFT) [7:0] TFT: Horizontal sync pulse width determines the HSYNC pulse's high

level width by counting the number of the VCLK.

0X00

WLH(STN) STN: WLH[1:0] bits determine the VLINE pulse's high level width by

counting the number of the HCLK.

WLH[7:2] are reserved.

00 = 16 HCLK, 01 = 32 HCLK,

10 = 48 HCLK, 11 = 64 HCLK