PROGRAMMER'S MODEL ARM920T PROCESSOR

2-22

Load a single entry into I TLB location 0, make it immune to Invalidate All and lock it down:

MCR to CP15 register 10, opcode_2 = 0x1, Base Value = 0, Current Victim = 0, P = 1

MCR I prefetch. Assuming an I TLB miss occurs, then entry 0 will be loaded.

MCR to CP15 register 10, opcode_2 = 0x1, Base Value = 1, Current Victim = 1, P = 0

Load a single entry into D TLB location 0, make it immune to Invalidate All and lock it down:

MCR to CP15 register 10, opcode_2 = 0x0, Base Value = 0, Current Victim = 0, P = 1

Data load (LDR/LDM) or store (STR/STM). Assuming a D TLB miss occurs, then entry 0 will be loaded.

MCR to CP15 register 10, opcode_2 = 0x0, Base Value = 1, Current Victim = 1, P = 0

REGISTERS 11-12 & 14: RESERVED

Accessing (reading or writing) any of these registers will cause unpredictable behavior.

REGISTER 13: PROCESS ID

Register 13 is the process identifier register. The process identifier register is 0x0 on reset.

Reading from CP15 register 13 returns the value of the process identifier. Writing CP15 register 13 updates the

process identifier to the value in bits [31:25]. Bits [24:0] should be zero.

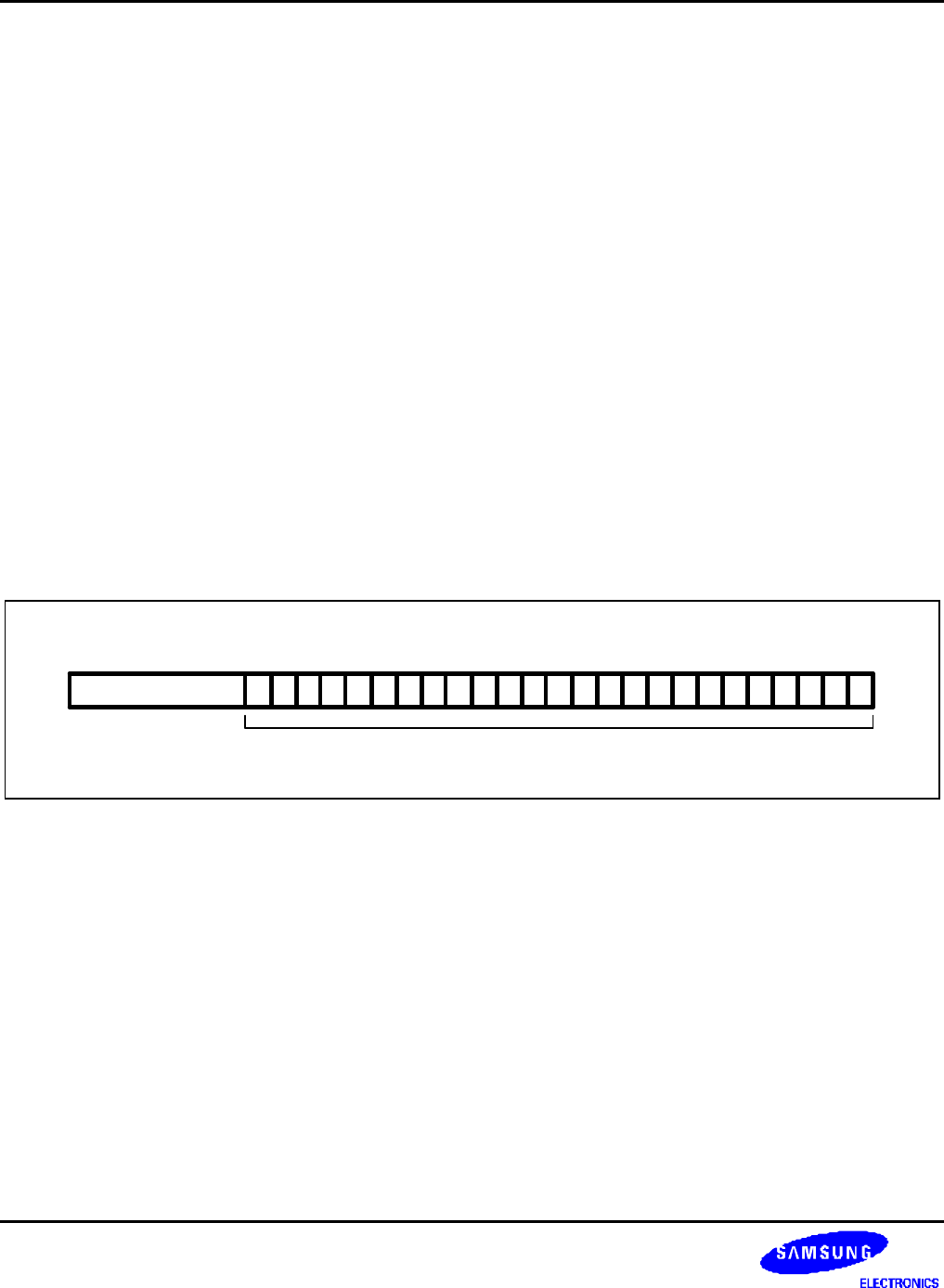

Register 13 bit assignments are shown in Figure 2-7.

31 19 1516 111221 20

0 0

8 7 4 3 0

0 0 0 0Proc ID 0

25 24 23 10 9 5

0 0 0 0

2 1

00000000

13141718

0 0 0

22

SBZ

6

0 0 0

Figure 2-7. Register 13

Register 13 can be accessed using the following instructions:

MRC p15, 0, Rd, c13, c0, 0 ;read process identifier

MCR p15, 0, Rd, c13, c0, 0 ;write process identifier