S3C2410A MMC/SD/SDIO HOST CONTROLLER

19-13

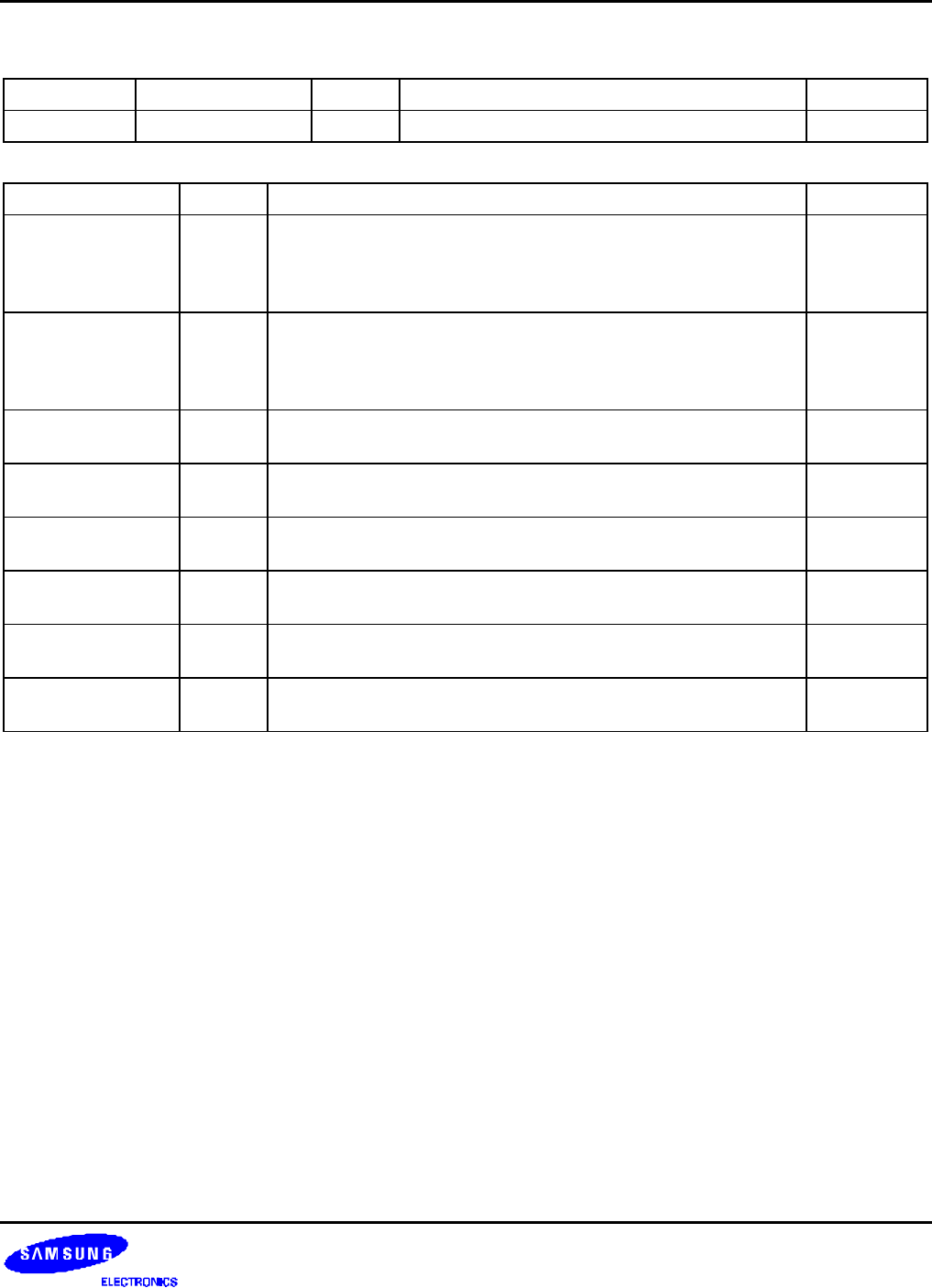

SDI FIFO Status (SDIFSTA) Register

Register Address R/W Description Reset Value

SDIFSTA 0x5A000038 R SDI FIFO status register 0x0

SDIFSTA Bit Description Initial State

FIFO available

Detect for Tx

(TFDET)

[13] Indicate that FIFO data is available for transmission when

DatMode (SDIDCON[12]) is data transmit mode. If DMA mode is

enable, SD host requests DMA operation.

0 = not detect (FIFO full), 1 = detect(0 ≤ FIFO ≤ 63)

0

FIFO available

Detect for Rx

(RFDET)

[12] Indicate that FIFO data is available for reception when DatMode

(SDIDCON[12]) is data receive mode. If DMA mode is enable, SD

host requests DMA operation.

0 = not detect(FIFO empty), 1 = detect(1 ≤ FIFO ≤ 64)

0

Tx FIFO Half Full

(TFHalf)

[11] Set to 1 whenever Tx FIFO is less than 33byte.

0 = 33 ≤ Tx FIFO ≤ 64, 1 = 0 ≤ Tx FIFO ≤ 32

0

Tx FIFO Empty

(TFEmpty)

[10] Set to 1 whenever Tx FIFO is empty.

0 = 1 ≤ Tx FIFO ≤ 64, 1 = Empty(0byte)

0

Rx FIFO Last Data

Ready (RFLast)

[9] Set to 1 whenever Rx FIFO has last data of all block.

0 = not received yet, 1 = Last data ready

0

Rx FIFO Full

(RFFull)

[8] Set to 1 whenever Rx FIFO is full.

0 = 0 ≤ Rx FIFO ≤ 63, 1 = Full(64byte)

0

Rx FIFO Half Full

(RFHalf)

[7] Set to 1 whenever Rx FIFO is more than 31byte.

0 = 0 ≤ Rx FIFO ≤ 31, 1 = 32 ≤ Rx FIFO ≤ 64

0

FIFO Count

(FFCNT)

[6:0] Number of data (byte) in FIFO 0000000