INTERRUPT CONTROLLER S3C2410A

14-4

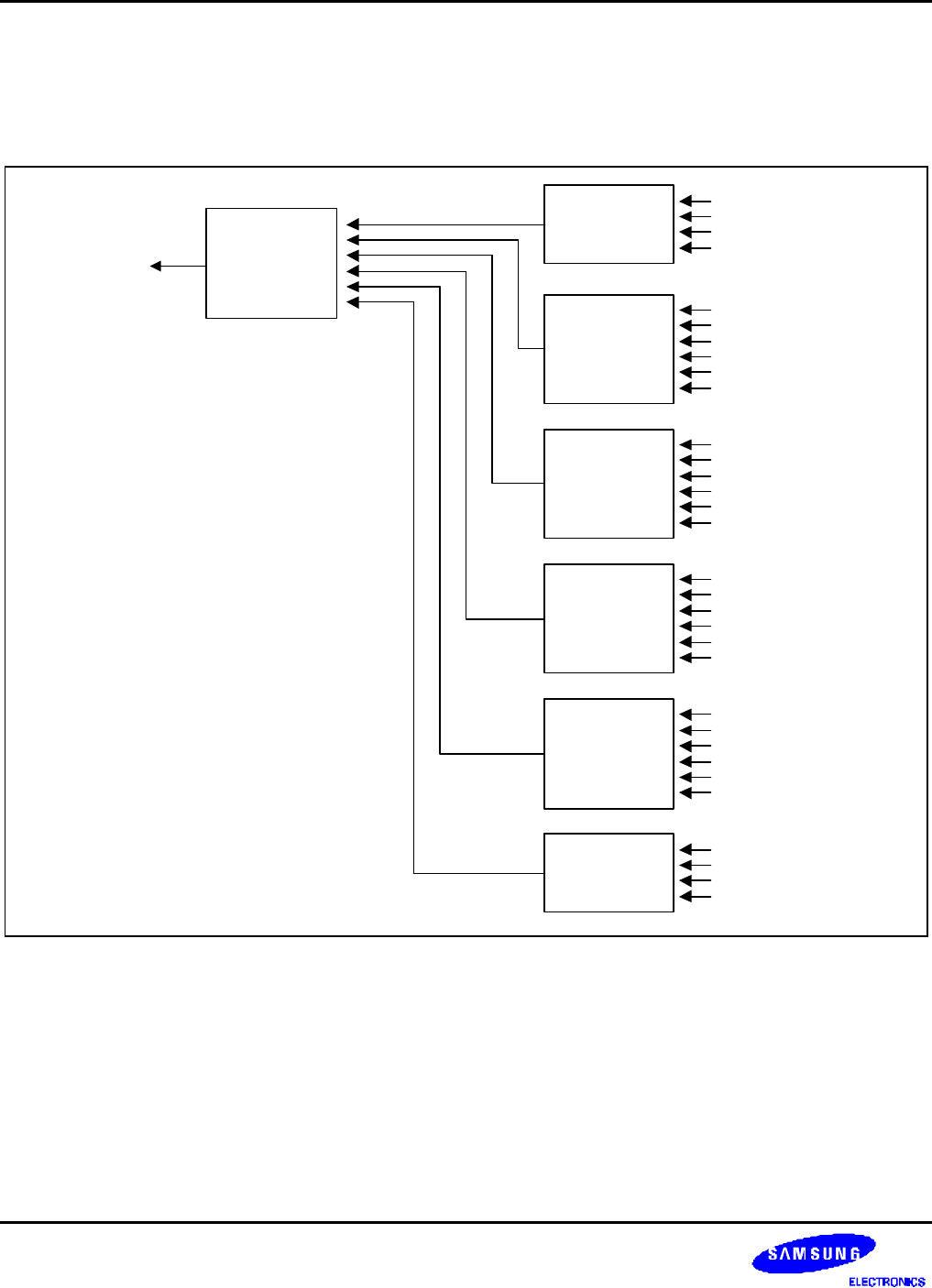

INTERRUPT PRIORITY GENERATING BLOCK

The priority logic for 32 interrupt requests is composed of seven rotation based arbiters: six first-level arbiters and one

second-level arbiter as shown in Figure 14-2 below.

ARBITER6

ARBITER0

ARM IRQ

REQ1/EINT0

ARBITER1

ARBITER2

ARBITER3

ARBITER4

ARBITER5

REQ4/INT_TICK

REQ5/INT_WDT

REQ0/INT_TIMER0

REQ3/INT_TIMER3

REQ2/INT_TIMER2

REQ1/INT_TIMER1

REQ4/INT_TIMER4

REQ0/INT_LCD

REQ1/INT_DMA0

REQ3/INT_DMA2

REQ2/INT_DMA1

REQ5/INT_UART2

REQ4/INT_DMA3

REQ5/INT_SDI

REQ0/INT_SPI0

REQ1/INT_UART1

REQ2/reserved

REQ3/INT_USBD

REQ4/INT_USBH

REQ5/INT_IIC

REQ1/INT_UART0

REQ2/INT_SPI1

REQ3/INT_RTC

REQ4/INT_ADC

REQ0

REQ1

REQ2

REQ3

REQ4

REQ5

REQ2/EINT1

REQ3/EINT2

REQ4/EINT3

REQ0/EINT4_7

REQ1/EINT8_23

REQ2/reserved

REQ3/nBATT_FLT

Figure 14-2. Priority Generating Block