ARM INSTRUCTION SET S3C2410A

3-30

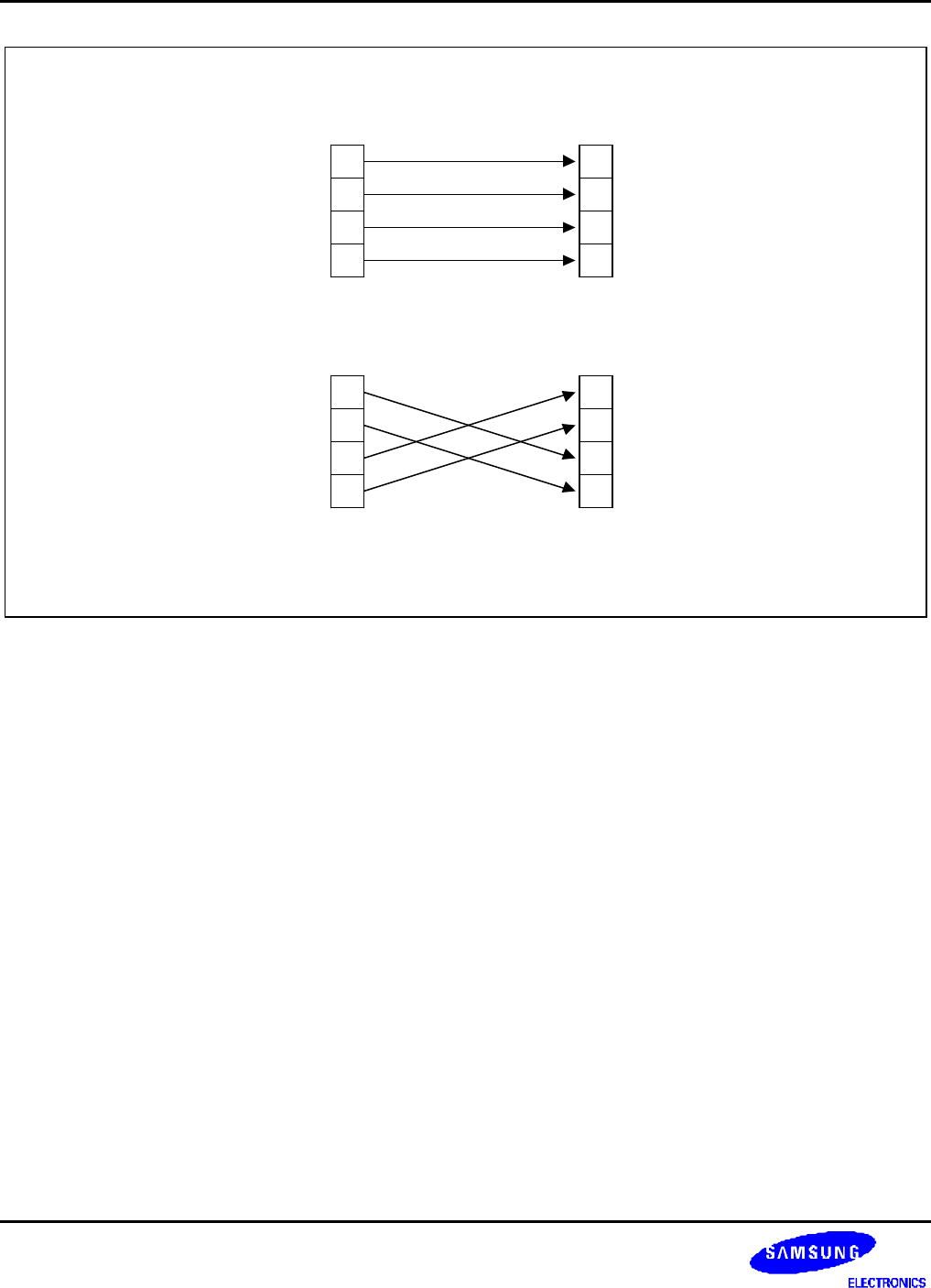

LDR from word aligned address

A+3

A

A+2

A+1

memory

24

16

8

0

A

B

C

D

register

24

16

8

0

A

B

C

D

LDR from address offset by 2

A+3

A

A+2

A+1

memory

24

16

8

0

A

B

C

D

register

24

16

8

0

A

B

C

D

Figure 3-15. Little-Endian Offset Addressing

Big-Endian Configuration

A byte load (LDRB) expects the data on data bus inputs 31 through 24 if the supplied address is on a word

boundary, on data bus inputs 23 through 16 if it is a word address plus one byte, and so on. The selected byte is

placed in the bottom 8 bits of the destination register and the remaining bits of the register are filled with zeros.

Please see Figure 2-1.

A byte store (STRB) repeats the bottom 8 bits of the source register four times across data bus outputs 31 through

0. The external memory system should activate the appropriate byte subsystem to store the data.

A word load (LDR) should generate a word aligned address. An address offset of 0 or 2 from a word boundary will

cause the data to be rotated into the register so that the addressed byte occupies bits 31 through 24. This means

that half-words accessed at these offsets will be correctly loaded into bits 16 through 31 of the register. A shift

operation is then required to move (and optionally sign extend) the data into the bottom 16 bits. An address offset of

1 or 3 from a word boundary will cause the data to be rotated into the register so that the addressed byte occupies

bits 15 through 8.

A word store (STR) should generate a word aligned address. The word presented to the data bus is not affected if the

address is not word aligned. That is, bit 31 of the register being stored always appears on data bus output 31.