UART S3C2410A

11-12

UART CONTROL REGISTER (Continued)

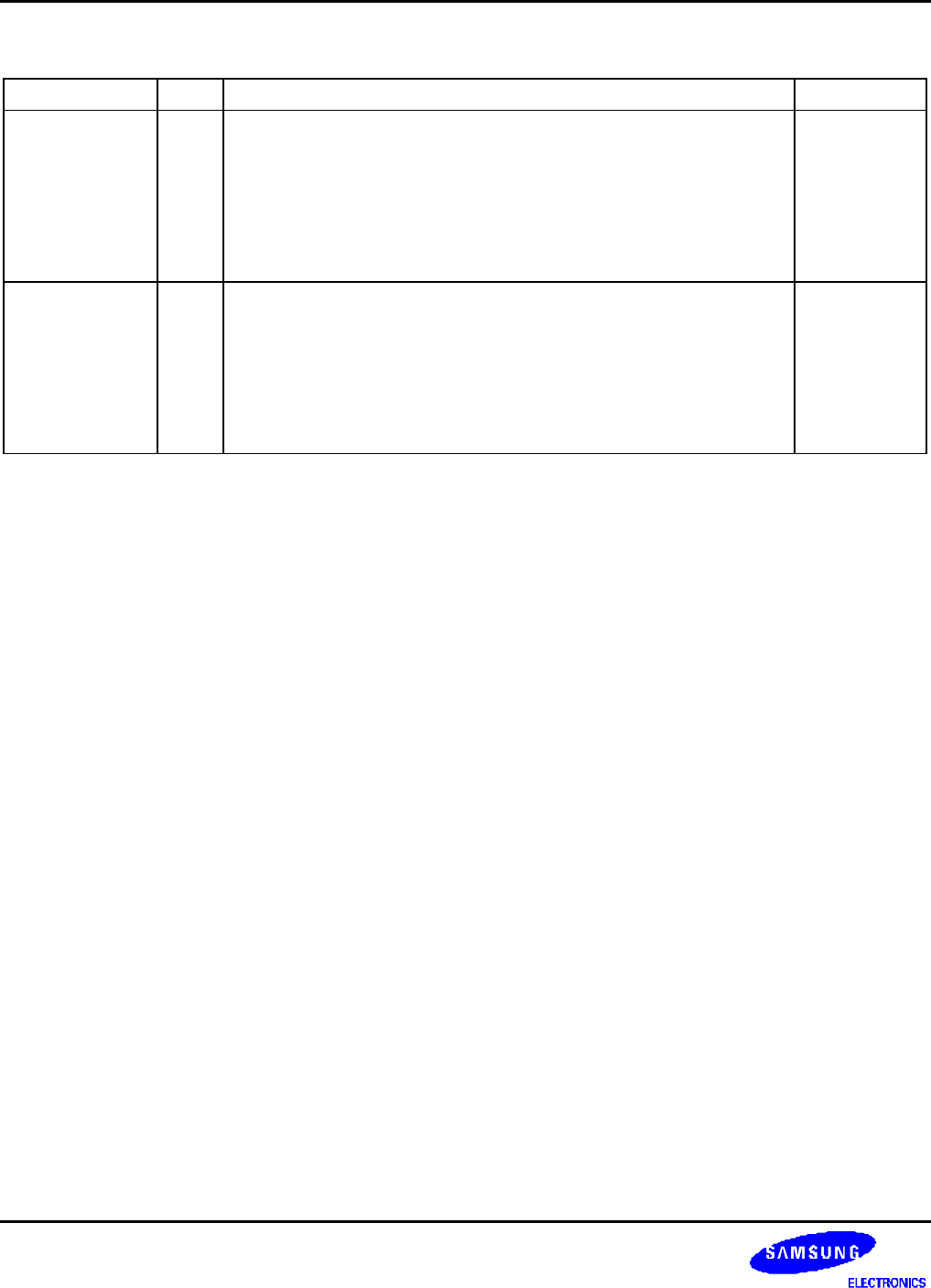

UCONn Bit Description Initial State

Transmit Mode [3:2] Determine which function is currently able to write Tx data to the

UART transmit buffer register. (UART Tx Enable/Disable)

00 = Disable

01 = Interrupt request or polling mode

10 = DMA0 request (Only for UART0),

DMA3 request (Only for UART2)

11 = DMA1 request (Only for UART1)

00

Receive Mode [1:0] Determine which function is currently able to read data from UART

receive buffer register. (UART Rx Enable/Disable)

00 = Disable

01 = Interrupt request or polling mode

10 = DMA0 request (Only for UART0),

DMA3 request (Only for UART2)

11 = DMA1 request (Only for UART1)

00

NOTE: When the UART does not reach the FIFO trigger level and does not receive data during 3 word time in DMA receive

mode with FIFO, the Rx interrupt will be generated (receive time out), and the users should check the FIFO status

and read out the rest.