PRODUCT OVERVIEW S3C2410A

1-24

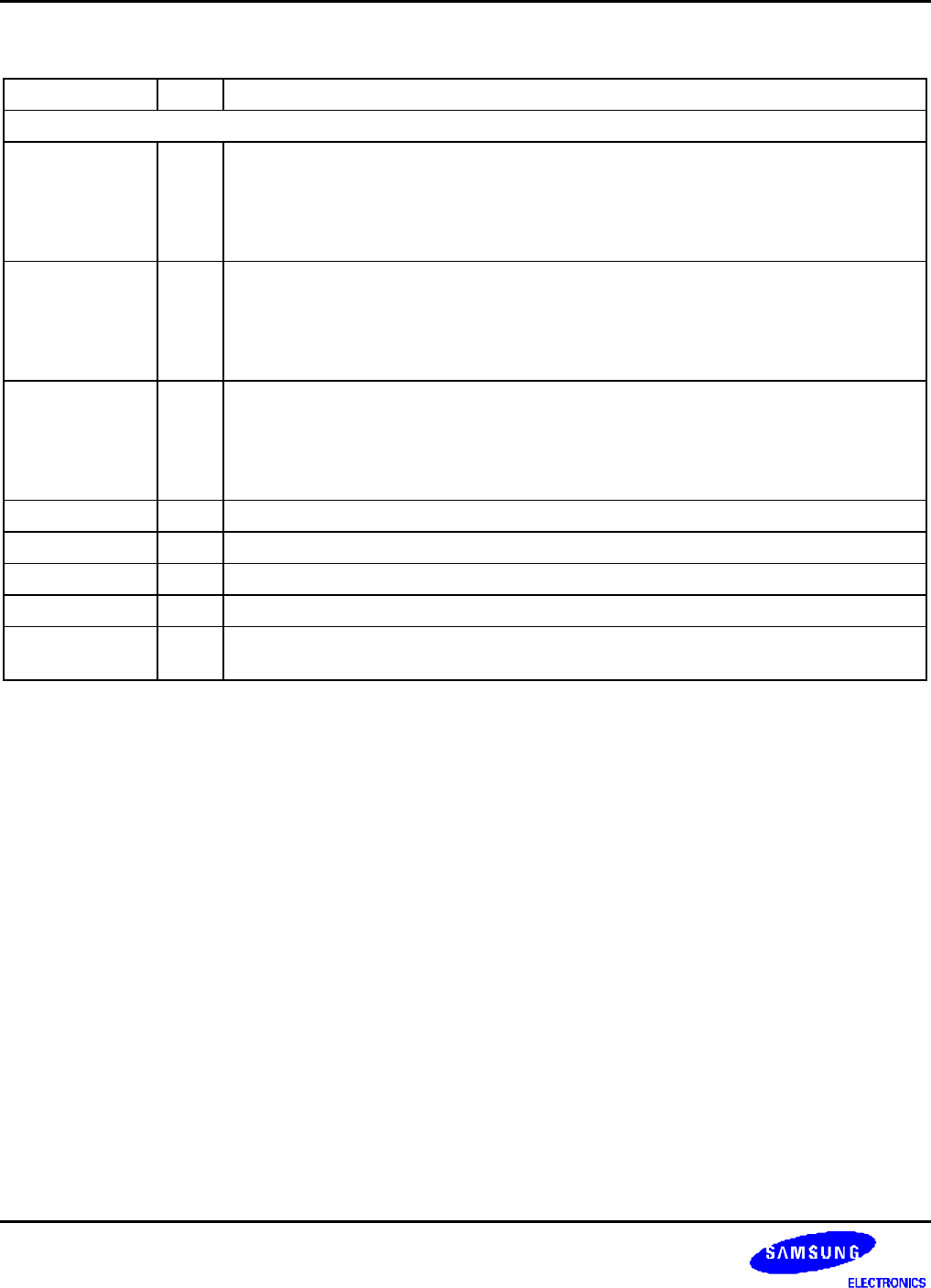

Table 1-3. S3C2410A Signal Descriptions (Continued)

Signal I/O Description

Reset, Clock & Power (Continued)

EXTCLK I External clock source.

When OM [3:2] = 11b, EXTCLK is used for MPLL CLK source and UPLL CLK source.

When OM [3:2] = 10b, EXTCLK is used for MPLL CLK source only.

When OM [3:2] = 01b, EXTCLK is used for UPLL CLK source only.

If it isn't used, it has to be High (3.3V).

XTIpll AI Crystal Input for internal osc circuit.

When OM [3:2] = 00b, XTIpll is used for MPLL CLK source and UPLL CLK source.

When OM [3:2] = 01b, XTIpll is used for MPLL CLK source only.

When OM [3:2] = 10b, XTIpll is used for UPLL CLK source only.

If it isn't used, XTIpll has to be High (3.3V).

XTOpll AO Crystal Output for internal osc circuit.

When OM [3:2] = 00b, XTIpll is used for MPLL CLK source and UPLL CLK source.

When OM [3:2] = 01b, XTIpll is used for MPLL CLK source only.

When OM [3:2] = 10b, XTIpll is used for UPLL CLK source only.

If it isn't used, it has to be a floating pin.

MPLLCAP AI Loop filter capacitor for main clock.

UPLLCAP AI Loop filter capacitor for USB clock.

XTIrtc AI 32.768 kHz crystal input for RTC. If it isn't used, it has to be in High (RTCVDD = 1.8V).

XTOrtc AO 32.768 kHz crystal output for RTC. If it isn't used, it has to be Float.

CLKOUT [1:0] O Clock output signal. The CLKSEL of MISCCR register configures the clock output

mode among the MPLL CLK, UPLL CLK, FCLK, HCLK and PCLK.