UART S3C2410A

11-16

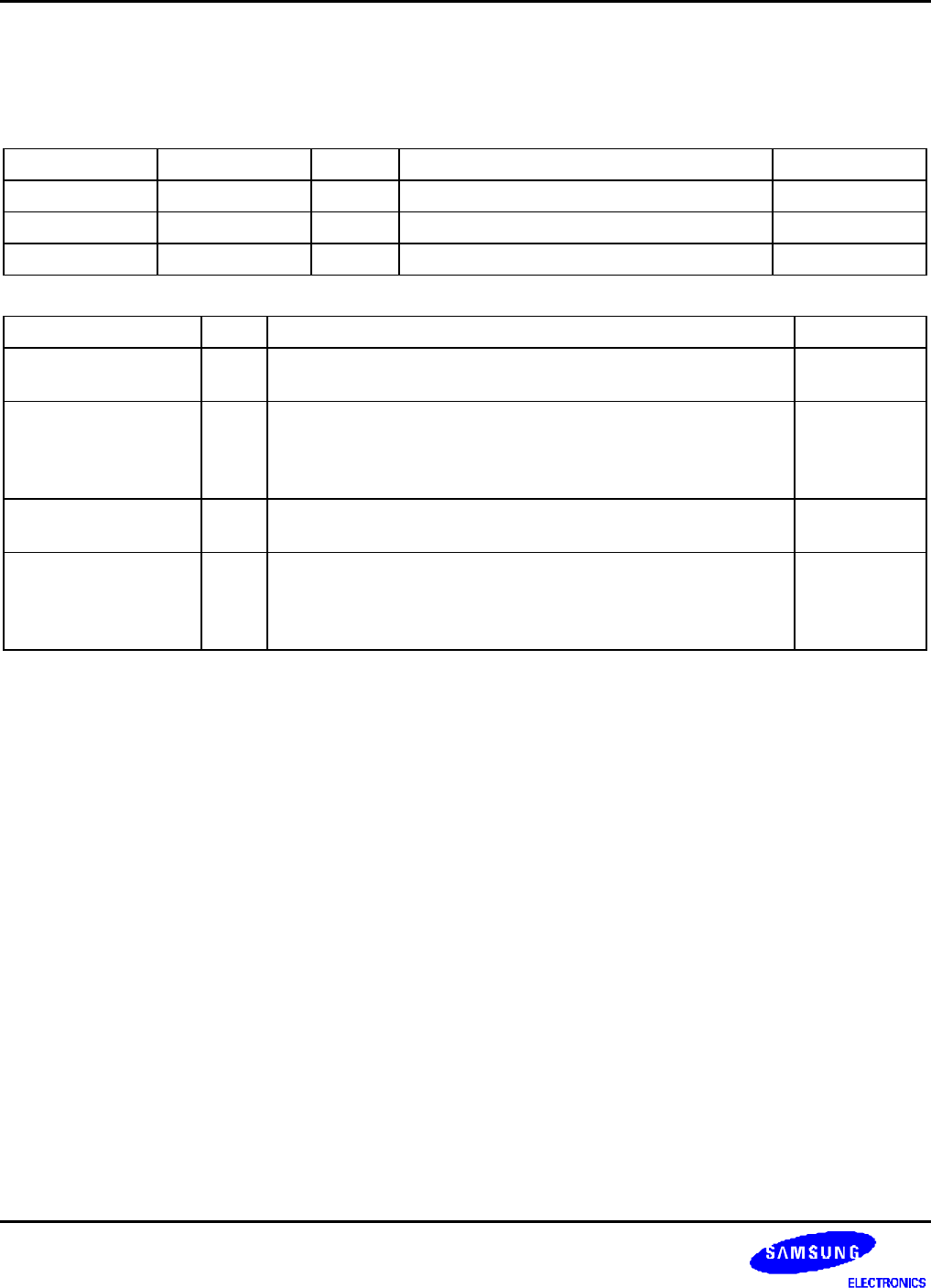

UART ERROR STATUS REGISTER

There are three UART Rx error status registers including UERSTAT0, UERSTAT1 and UERSTAT2 in the UART

block.

Register Address R/W Description Reset Value

UERSTAT0 0x50000014 R UART channel 0 Rx error status register 0x0

UERSTAT1 0x50004014 R UART channel 1 Rx error status register 0x0

UERSTAT2 0x50008014 R UART channel 2 Rx error status register 0x0

UERSTATn Bit Description Initial State

Reserved [3] 0 = No frame error during receive

1 = Frame error (Interrupt is requested.)

0

Frame Error [2] Set to 1 automatically whenever a frame error occurs during

receive operation.

0 = No frame error during receive

1 = Frame error (Interrupt is requested.)

0

Reserved [1] 0 = No frame error during receive

1 = Frame error (Interrupt is requested.)

0

Overrun Error [0] Set to 1 automatically whenever an overrun error occurs during

receive operation.

0 = No overrun error during receive

1 = Overrun error (Interrupt is requested.)

0

NOTE: These bits (UERSATn[3:0]) are automatically cleared to 0 when the UART error status register is read.