ARM920T PROCESSOR PROGRAMMER'S MODEL

2-15

REGISTER 6: FAULT ADDRESS REGISTER

Register 6 is the fault address register (FAR) which contains the modified virtual address of the access being

attempted when the last fault occurred. The FAR is only updated for data faults, not for prefetch faults.

(The address for a prefetch fault can be found in R14.)

The following instructions can be used to access the FAR:

MRC p15, 0, Rd, c6, c0, 0 ;read FAR data

MCR p15, 0, Rd, c6, c0, 0 ;write FAR data

The ability to write to the FAR is intended for a debugger to restore a previous state.

REGISTER 7: CACHE OPERATIONS

Register 7 is a write-only register used to manage the instruction and data caches, ICache and DCache.

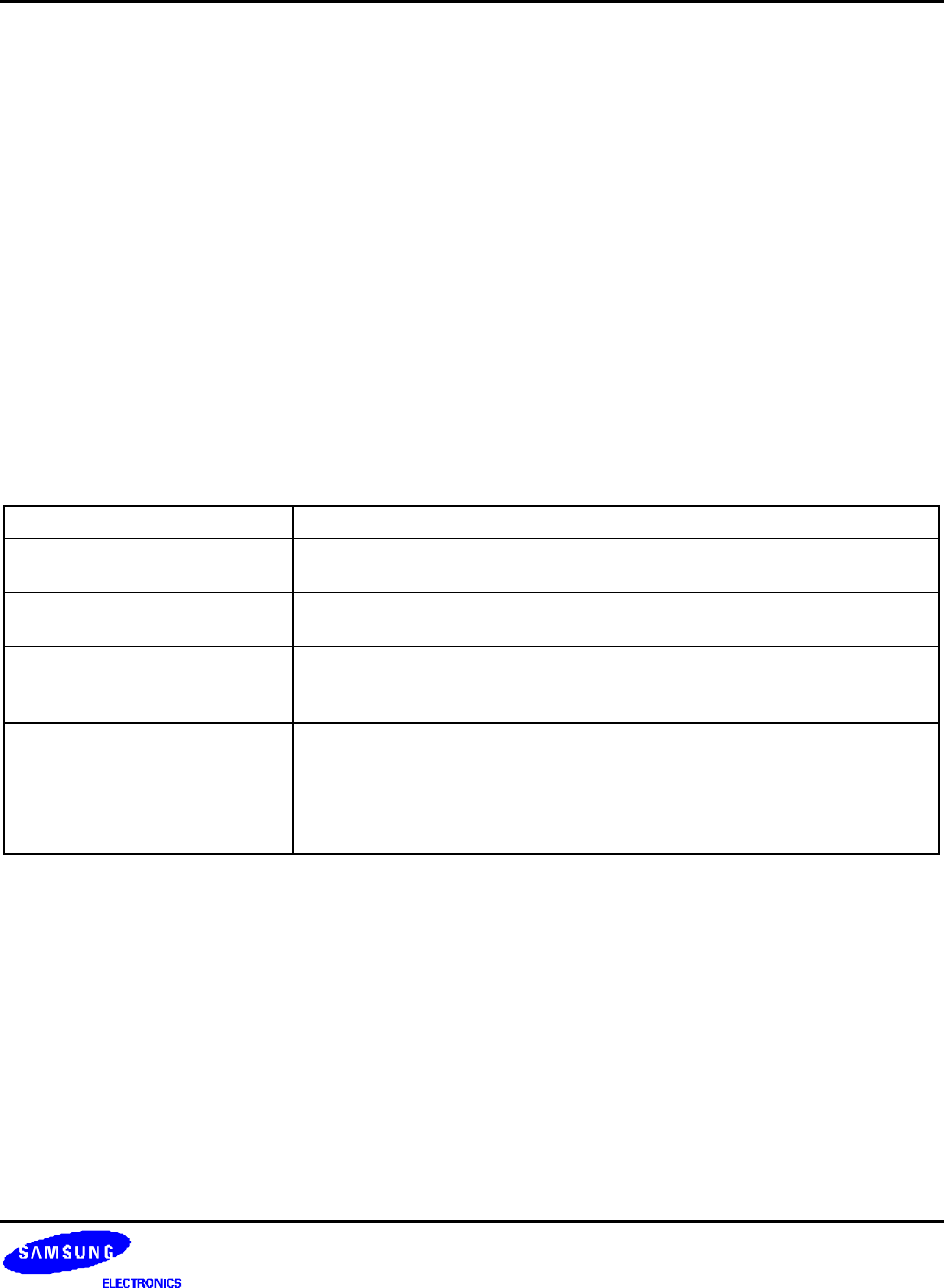

The cache operations provided by register 7 are described in Table 2-15.

Table 2-15. Function Descriptions Register 7

Function Description

Invalidate cache Invalidates all cache data, including any dirty data (note).

Use with caution.

Invalidate single entry using

modified virtual address

Invalidates a single cache line, discarding any dirty data (note).

Use with caution.

Clean D single entry using either

index or modified virtual address

Writes the specified cache line to main memory if the line is marked valid and

dirty and marks the line as not dirty (note).

The valid bit is unchanged.

Clean and Invalidate D entry using

either index or modified virtual

address

Writes the specified cache line to main memory if the line is marked valid and

dirty (note).

The line is marked not valid.

Prefetch cache line Performs an ICache lookup of the specified modified virtual address.

If the cache misses, and the region is cacheable, a linefill will be performed.

NOTE: Dirty data is data that has been modified in the cache but not yet written to main memory.