ARM INSTRUCTION SET S3C2410A

3-28

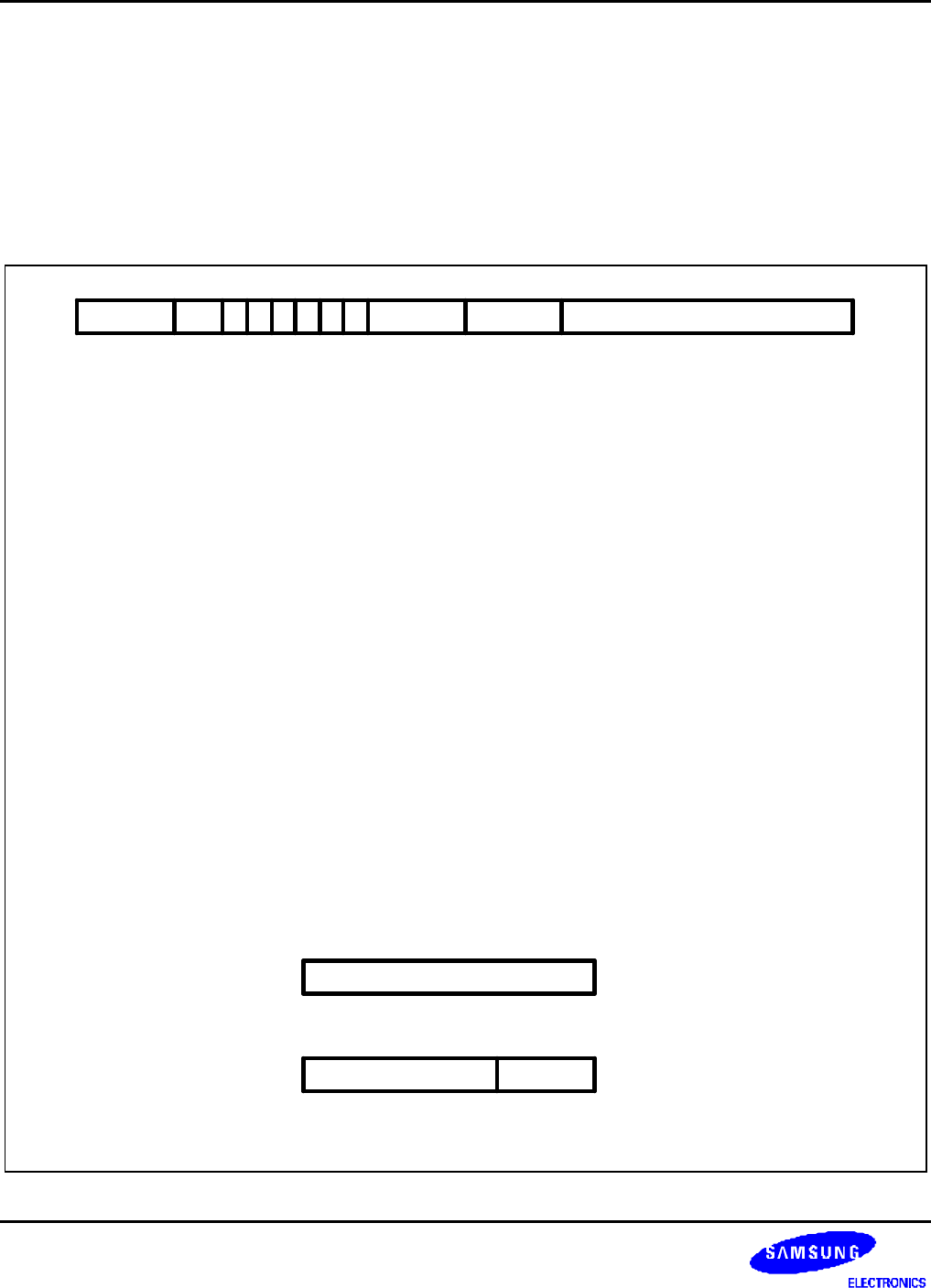

SINGLE DATA TRANSFER (LDR, STR)

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-14.

The single data transfer instructions are used to load or store single bytes or words of data. The memory address

used in the transfer is calculated by adding an offset to or subtracting an offset from a base register.

The result of this calculation may be written back into the base register if auto-indexing is required.

31 27 19 15 0

Cond

28 16 11122123

B

20

L Rn Rd

22

01 I P U OffsetW

26 2425

[15:12] Source/Destination Registers

[19:16] Base Register

[20] Load/Store Bit

0 = Store to memory

1 = Load from memory

[21] Write-back Bit

0 = No write-back

1 = Write address into base

[22] Byte/Word Bit

0 = Transfer word quantity

1 = Transfer byte quantity

[23] Up/Down Bit

0 = Down: subtract offset from base

1 = Up: add offset to base

[24] Pre/Post Indexing Bit

0 = Post: add offset after transfer

1 = Pre: add offset before transfer

[25] Immediate Offset

0 = Offset is an immediate value

[11:0] Offset

Shift

Immediate

[11:0] Unsigned 12-bit immediate offset

11

11

Rm

[3:0] Offset register [11:4] Shift applied to Rm

[31:28] Condition Field

0

4 3 0

Figure 3-14. Single Data Transfer Instructions