PROGRAMMER'S MODEL ARM920T PROCESSOR

2-2

ABOUT THE ARM9TDMI PROGRAMMER'S MODEL

The ARM9TDMI processor core implements ARM v4T architecture, and so executes the ARM 32-bit instruction set

and the compressed Thumb 16-bit instruction set. The programmer's model is fully described in the ARM

Architecture Reference Manual. The ARM9TDMI Technical Reference Manual gives implementation details including

instruction execution cycle times.

The ARM v4T architecture specifies a small number of implementation options. The options selected in the

ARM9TDMI implementation are listed in Table 2-1. For comparison, the options selected for the ARM7TDMI

implementation are also shown

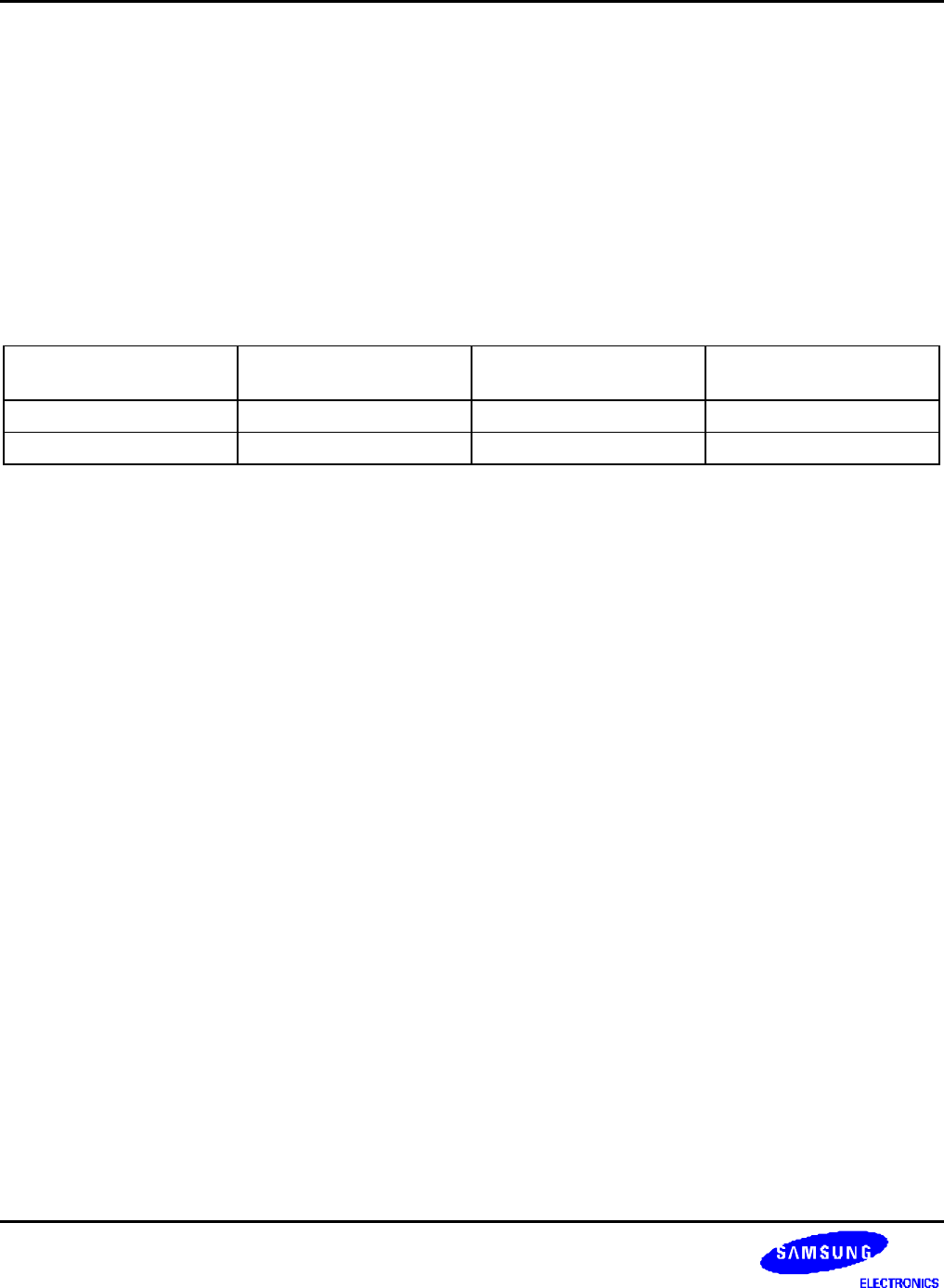

Table 2-1. ARM9TDMI Implementation Option

Processor core ARM architecture Data abort model Value stored by direct

STR, STRT, STM of PC

ARM7TDMI v4T Base updated Address of Inst + 12

ARM9TDMI v4T Base restored Address of Inst + 12

The ARM9TDMI is code-compatible with the ARM7TDMI, with two exceptions:

• The ARM9TDMI implements the base restored data abort model, which significantly simplifies the software data

abort handler.

• The ARM9TDMI fully implements the instruction set extension spaces added to the ARM (32-bit) instruction set

in architecture v4 and v4T.

These differences are explained in more detail below.

DATA ABORT MODEL

The base restored data abort model differs from the base updated data abort model implemented by ARM7TDMI.

The difference in the data abort model affects only a very small section of operating system code, the data abort

handler. It does not affect user code. With the base restored data abort model, when a data abort exception occurs

during the execution of a memory access instruction, the base register is always restored by the processor hardware

to the value the register contained before the instruction was executed. This removes the need for the data abort

handler to unwind any base register update which may have been specified by the aborted instruction.