S3C2410A ARM INSTRUCTION SET

3-9

DATA PROCESSING

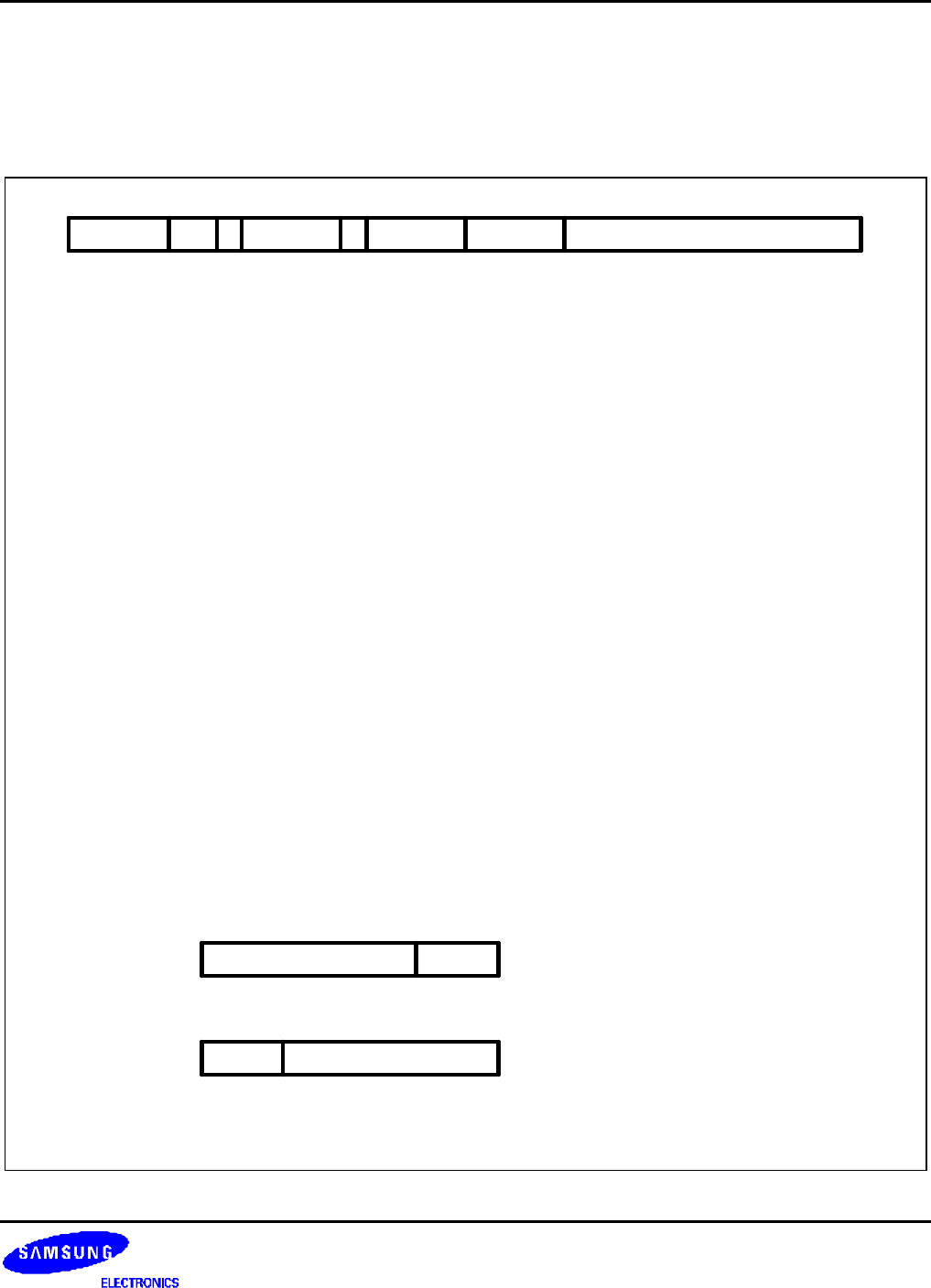

The data processing instruction is only executed if the condition is true. The conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-4.

31 2427 19 15

Cond Operand2

28 16 111221

[15:12] Destination register

0 = Branch 1 = Branch with link

[19:16] 1st operand register

0 = Branch 1 = Branch with link

[20] Set condition codes

0 = Do not after condition codes 1 = Set condition codes

[24:21] Operation codes

0000 = AND-Rd: = Op1 AND Op2

0001 = EOR-Rd: = Op1 EOR Op2

0010 = SUB-Rd: = Op1-Op2

0011 = RSB-Rd: = Op2-Op1

0100 = ADD-Rd: = Op1+Op2

0101 = ADC-Rd: = Op1+Op2+C

0110 = SBC-Rd: = OP1-Op2+C-1

0111 = RSC-Rd: = Op2-Op1+C-1

1000 = TST-set condition codes on Op1 AND Op2

1001 = TEO-set condition codes on OP1 EOR Op2

1010 = CMP-set condition codes on Op1-Op2

1011 = SMN-set condition codes on Op1+Op2

1100 = ORR-Rd: = Op1 OR Op2

1101 = MOV-Rd: =Op2

1110 = BIC-Rd: = Op1 AND NOT Op2

1111 = MVN-Rd: = NOT Op2

[25] Immediate operand

0 = Operand 2 is a register 1 = Operand 2 is an immediate value

[11:0] Operand 2 type selection

26 25

00 L

20

OpCode S Rn Rd

0

Rotate

Shift

Rm

[3:0] 2nd operand register [11:4] Shift applied to Rm

311 04

811 07

Imm

[7:0] Unsigned 8 bit immediate value [11:8] Shift applied to Imm

[31:28] Condition field

Figure 3-4. Data Processing Instructions