IIS-BUS INTERFACE S3C2410A

21-4

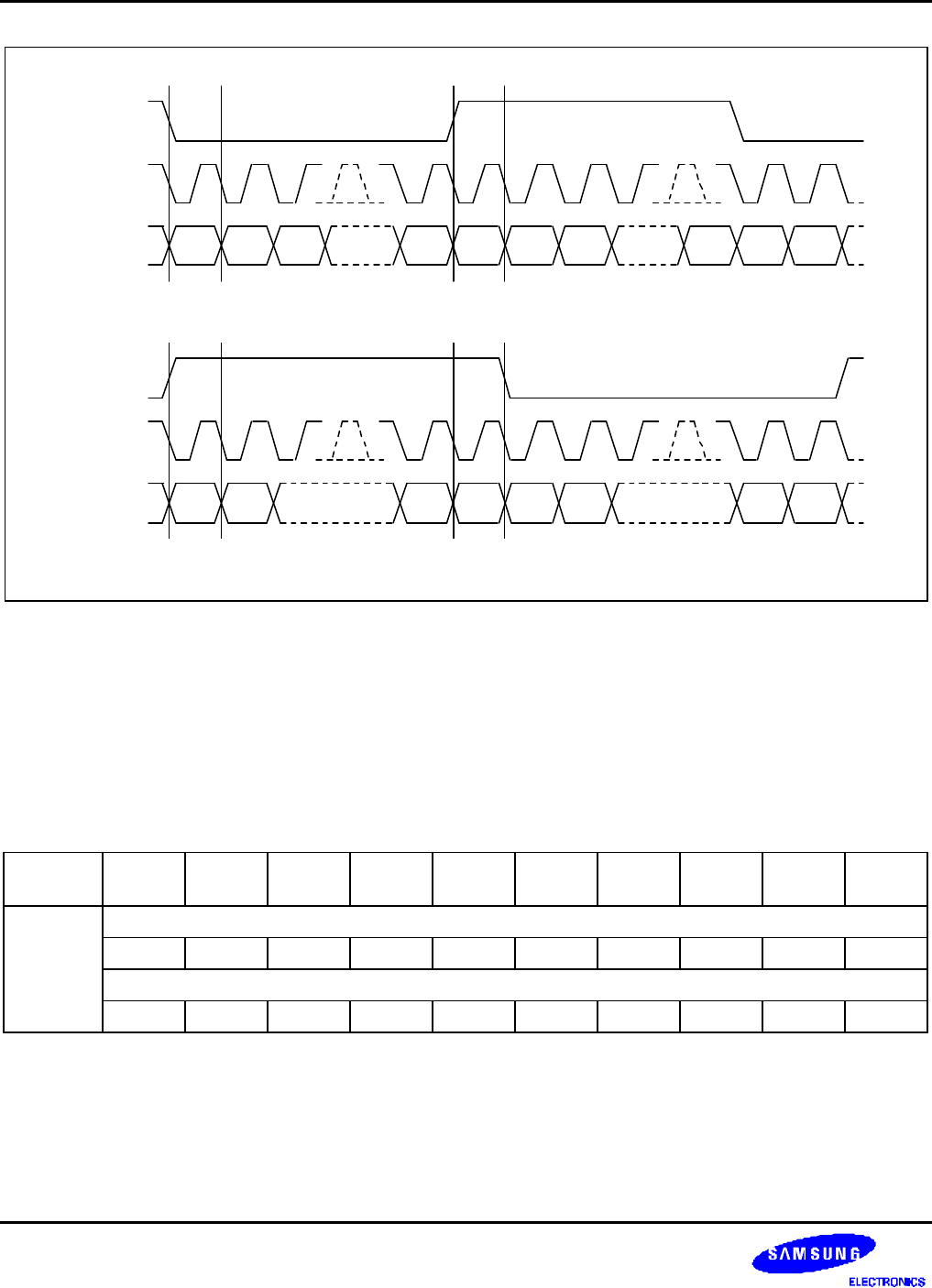

IIS-bus Format (N=8 or 16)

MSB

(1st)

2nd

Bit

N-1th

Bit

LSB

(last)

MSB

(1st)

2nd

Bit

N-1th

Bit

LSB

(last)

MSB

(1st)

LRCK

SCLK

SD

LEFT RIGHT LEFT

MSB-justified Format (N=8 or 16)

2nd

Bit

N-1th

Bit

LSB

(last)

MSB

(1st)

2nd

Bit

N-1th

Bit

LSB

(last)

LRCK

SCLK

SD

LEFT RIGHT

MSB

(1st)

Figure 21-2. IIS-Bus and MSB (Left)-justified Data Interface Formats

SAMPLING FREQUENCY AND MASTER CLOCK

Master clock frequency (PCLK) can be selected by sampling frequency as shown in Table 21-1. Because PCLK is

made by IIS prescaler, the prescaler value and PCLK type (256 or 384fs) should be determined properly. Serial bit

clock frequency type (16/32/48fs) can be selected by the serial bit per channel and PCLK as shown in Table 21-2.

Table 21-1. CODEC clock (CODECLK = 256 or 384fs)

IISLRCK

(fs)

8.000

kHz

11.025

kHz

16.000

kHz

22.050

kHz

32.000

kHz

44.100

kHz

48.000

kHz

64.000

kHz

88.200

kHz

96.000

kHz

256fs

CODECLK 2.0480 2.8224 4.0960 5.6448 8.1920 11.2896 12.2880 16.3840 22.5792 24.5760

(MHz) 384fs

3.0720 4.2336 6.1440 8.4672 12.2880 16.9344 18.4320 24.5760 33.8688 36.8640