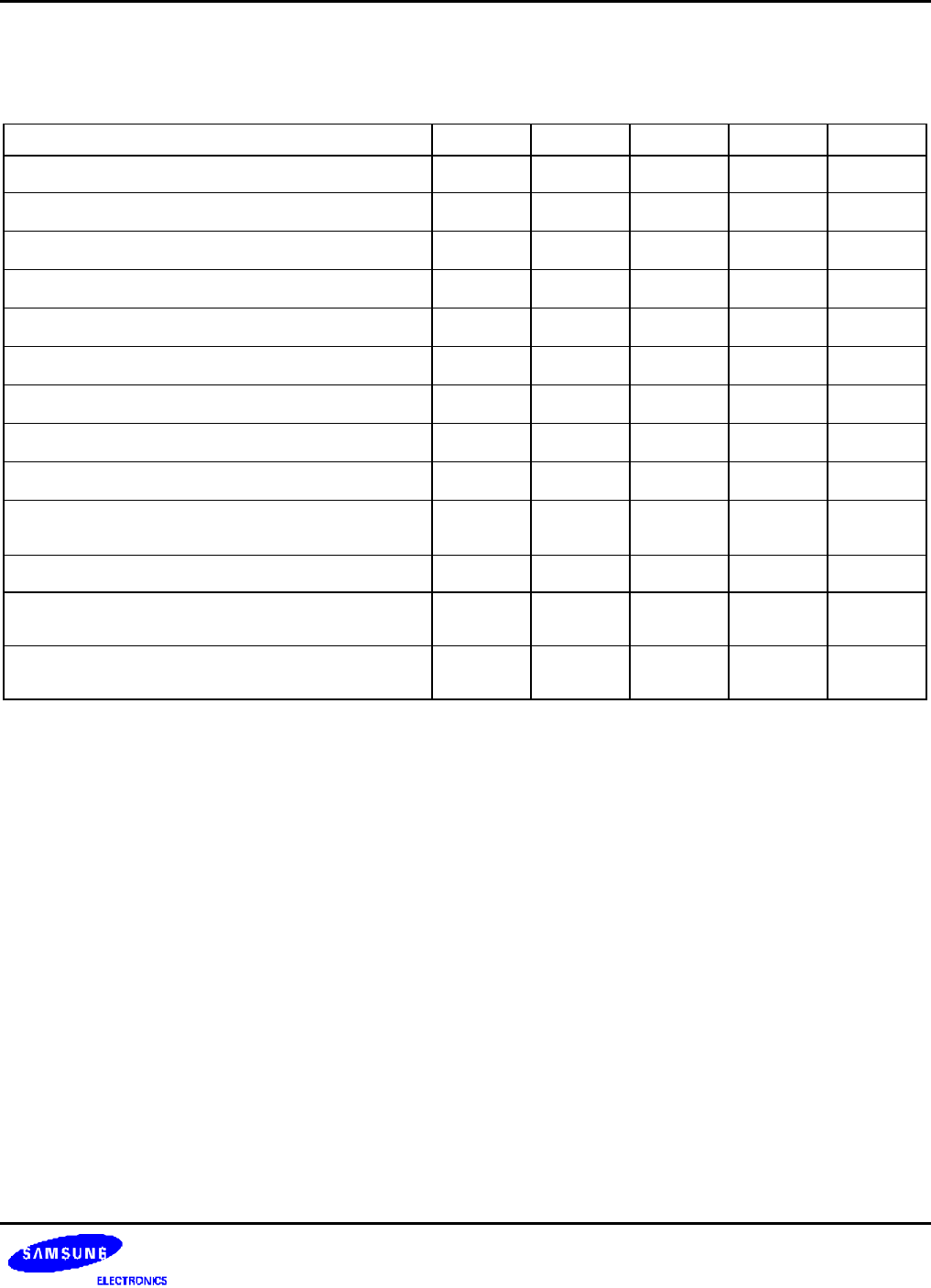

S3C2410A ELECTRICAL DATA

24-31

Table 24-6. Clock Timing Constants

(V

DDi

=V

DDalive

=V

DDiarm

= 1.8V ± 0.15 / 2.0 V ± 0.1 V, T

A

= -40 to 85 °C, V

DDMOP

= 3.3V ± 0.3V)

Parameter Symbol Min Typ Max Unit

Crystal clock input frequency f

XTAL

10 – 20 MHz

Crystal clock input cycle time t

XTALCYC

50 – 100 ns

External clock input frequency f

EXT

– – 66 MHz

External clock input cycle time t

EXTCYC

15 – – ns

External clock input low level pulse width t

EXTLOW

7 – – ns

External clock to HCLK (without PLL) t

EX2HC

3 – 9 ns

HCLK (internal) to CLKOUT t

HC2CK

3 – 11 ns

HCLK (internal) to SCLK t

HC2SCLK

0 – 3 ns

External clock input high level pulse width t

EXTHIGH

4 – – ns

Reset assert time after clock stabilization t

RESW

4 – – XTIpll or

EXTCLK

PLL Lock Time t

PLL

200 – uS

Power_OFF mode return oscillation setting time t

OSC2

– – 65536 XTIpll or

EXTCLK

The interval before CPU runs after nRESET is

released.

t

RST2RUN

– 7 – XTIpll or

EXTCLK