UART S3C2410A

11-20

UART BAUD RATE DIVISOR REGISTER

There are three UART baud rate divisor registers including UBRDIV0, UBRDIV1 and UBRDIV2 in the UART block.

The value stored in the baud rate divisor register (UBRDIVn), is used to determine the serial Tx/Rx clock rate (baud

rate) as follows:

UBRDIVn = (int)(PCLK / (bps x 16) ) –1

or

UBRDIVn = (int)(UEXTCLK / (bps x 16) ) –1

Where, the divisor should be from 1 to (2

16

-1) and UEXTCLK should be smaller than PCLK.

For example, if the baud-rate is 115200 bps and PCLK or UEXTCLK is 40 MHz, UBRDIVn is:

UBRDIVn = (int)(40000000 / (115200 x 16) ) -1

= (int)(21.7) -1

= 21 -1 = 20

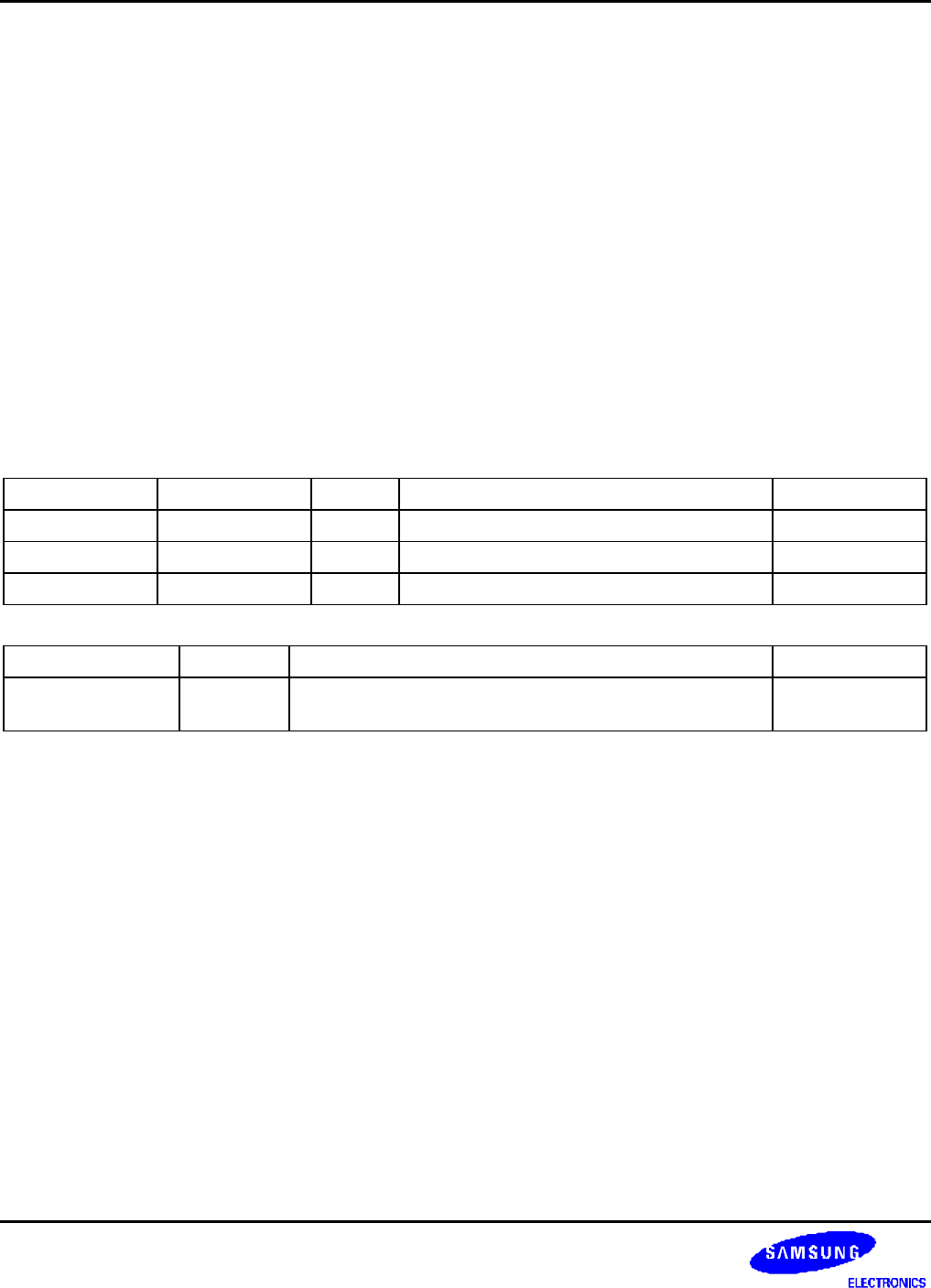

Register Address R/W Description Reset Value

UBRDIV0 0x50000028 R/W Baud rate divisior register 0 –

UBRDIV1 0x50004028 R/W Baud rate divisior register 1 –

UBRDIV2 0x50008028 R/W Baud rate divisior register 2 –

UBRDIVn Bit Description Initial State

UBRDIV [15:0] Baud rate division value

UBRDIVn > 0

–