MMU ARM920T PROCESSOR

3-18

FAULT ADDRESS AND FAULT STATUS REGISTERS

On a data abort, the MMU places an encoded 4 bit value, FS[3:0], along with the 4-bit encoded domain number, in

the Data fault status register (FSR). Similarly, on a prefetch abort, in the Prefetch fault status register, intended for

debug purposes only. In addition, the modified virtual address associated with the data abort is latched into the fault

address register (FAR). If an access violation simultaneously generates more than one source of abort, they are

encoded in the priority given in Table 3-4 . The fault address register is not updated by faults caused by instruction

prefetches.

FAULT STATUS

The remainder of this chapter describes the various access permissions and controls supported by the data MMU

and details how these are interpreted to generate faults.

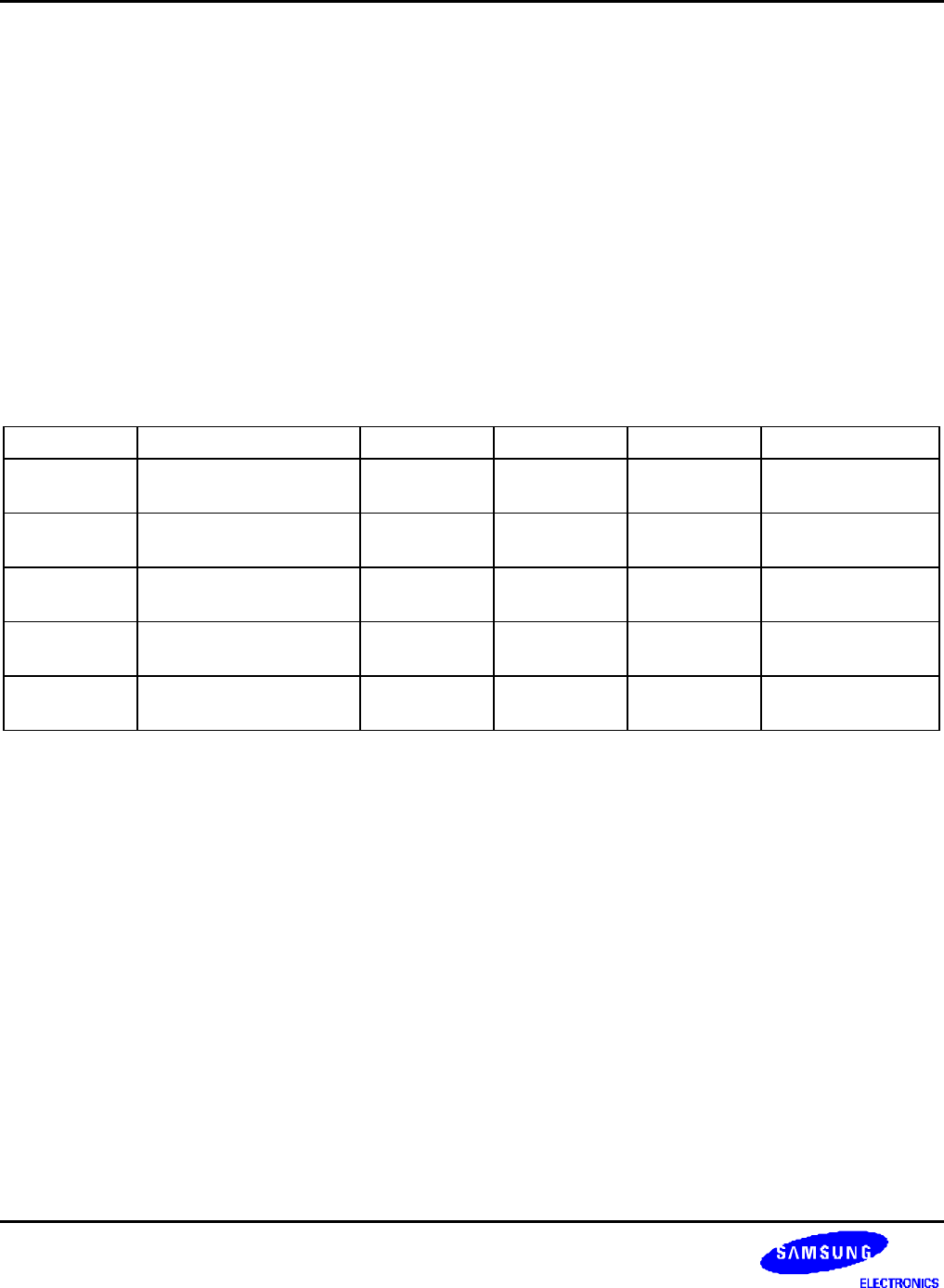

Table 3-4. Priority Encoding of Fault Status

Source Status Domain FAR

Highest

priority

Alignment 0b00x1 invalid MVA of access

causing abort

Translation Section Page 0b0101

0b0111

invalid

valid

MVA of access

causing abort

Domain Section Page 0b1001

0b1011

valid

valid

MVA of access

causing abort

Permission Section Page 0b1101

0b1111

valid

valid

MVA of access

causing abort

Lowest priority External abort on NCNB

access or NCB read.

Section Page 0b1000

0b1010

valid

valid

MVA of access

causing abort

NOTES:

1. Data FSR only.

Alignment faults may write either 0b0001 or 0b0011 into FS[3:0].

Invalid values in domain[3:0] occur because the fault is raised before a valid domain field has been read from a page

table descriptor.

Any abort masked by the priority encoding may be regenerated by fixing the primary abort and restarting the instruction.

NCNB means Non-Cacheable and Non-Bufferable.

NCB means Non-Cacheable but Bufferable.

2. Instruction FSR only.

The same priority applies as for the Data fault status register, except that alignment faults cannot occur, and external

aborts apply only to NC (Non-cacheable) reads.