CLOCK & POWER MANAGEMENT S3C2410A

7-20

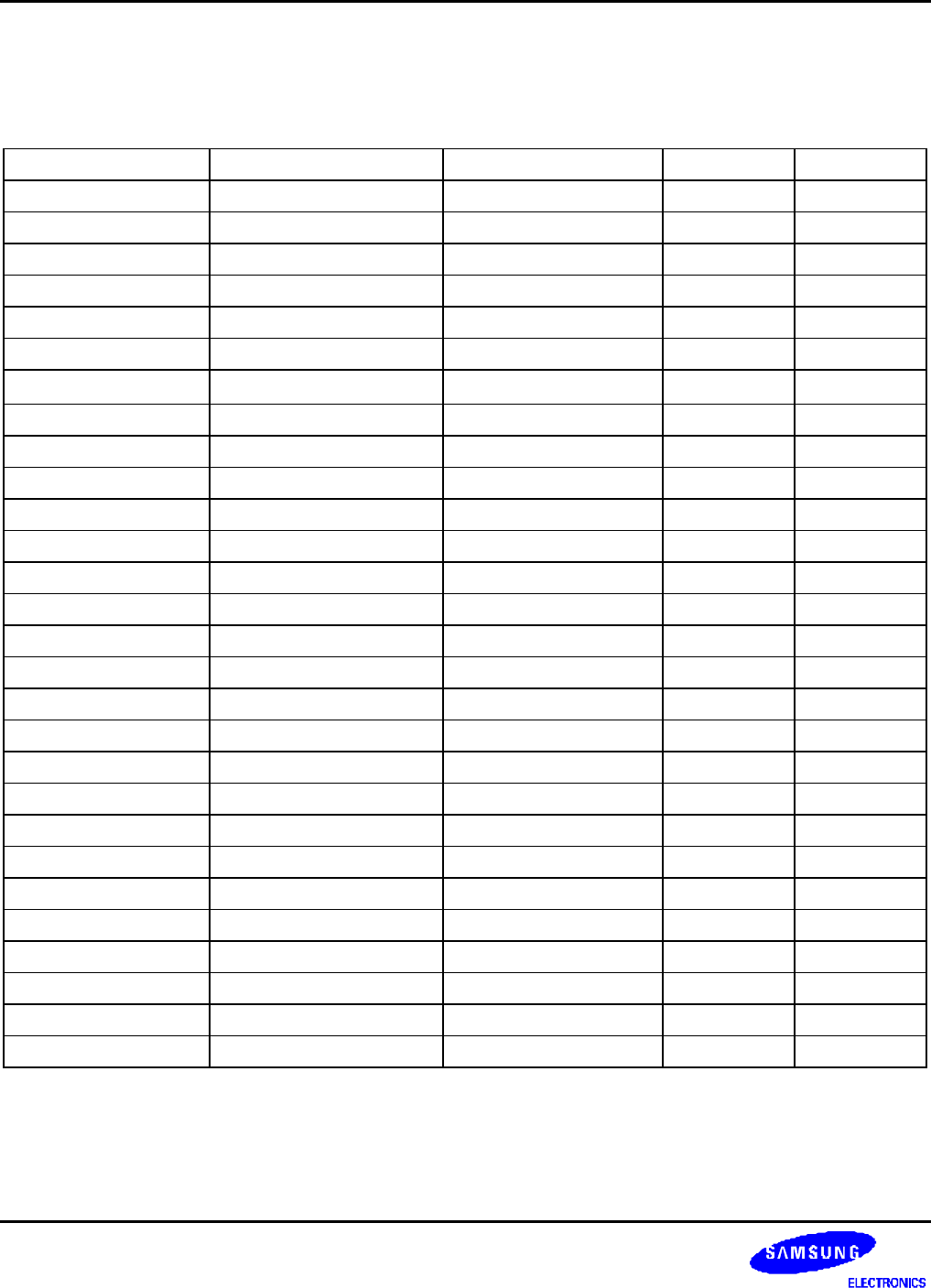

PLL VALUE SELECTION TABLE

It is not easy to find a proper PLL value. So, We recommend referring to the following PLL value recommendation

table.

Input Frequency Output Frequency MDIV PDIV SDIV

12.00MHz 11.289MHz N/A N/A N/A

12.00MHz 16.934MHz N/A N/A N/A

12.00MHz 22.50MHz N/A N/A N/A

12.00MHz 33.75MHz 82 (0x52) 2 3

12.00MHz 45.00MHz 82 (0x52) 1 3

12.00MHz 50.70MHz 161 (0xa1) 3 3

12.00Mhz

48.00Mhz

(note)

120 (0x78) 2 3

12.00MHz 56.25MHz 142 (0x8e) 2 3

12.00MHz 67.50MHz 82 (0x52) 2 2

12.00MHz 79.00MHz 71 (0x47) 1 2

12.00MHz 84.75MHz 105 (0x69) 2 2

12.00MHz 90.00MHz 112 (0x70) 2 2

12.00MHz 101.25MHz 127 (0x7f) 2 2

12.00MHz 113.00MHz 105 (0x69) 1 2

12.00MHz 118.50MHz 150 (0x96) 2 2

12.00MHz 124.00MHz 116 (0x74) 1 2

12.00MHz 135.00MHz 82 (0x52) 2 1

12.00MHz 147.00MHz 90 (0x5a) 2 1

12.00MHz 152.00MHz 68 (0x44) 1 1

12.00MHz 158.00MHz 71 (0x47) 1 1

12.00MHz 170.00MHz 77 (0x4d) 1 1

12.00MHz 180.00MHz 82 (0x52) 1 1

12.00MHz 186.00MHz 85 (0x55) 1 1

12.00MHz 192.00MHz 88 (0x58) 1 1

12.00MHz 202.80MHz 161 (0xa1) 3 1

12.00MHz 266.00MHz 125 (0x7d) 1 1

12.00MHz 268.00MHz 126 (0x7e) 1 1

12.00MHz 270.00MHz 127 (0x7f) 1 1

NOTE: The 48.00MHz output is used for UPLLCON register.