S3C2410A LCD CONTROLLER

15-3

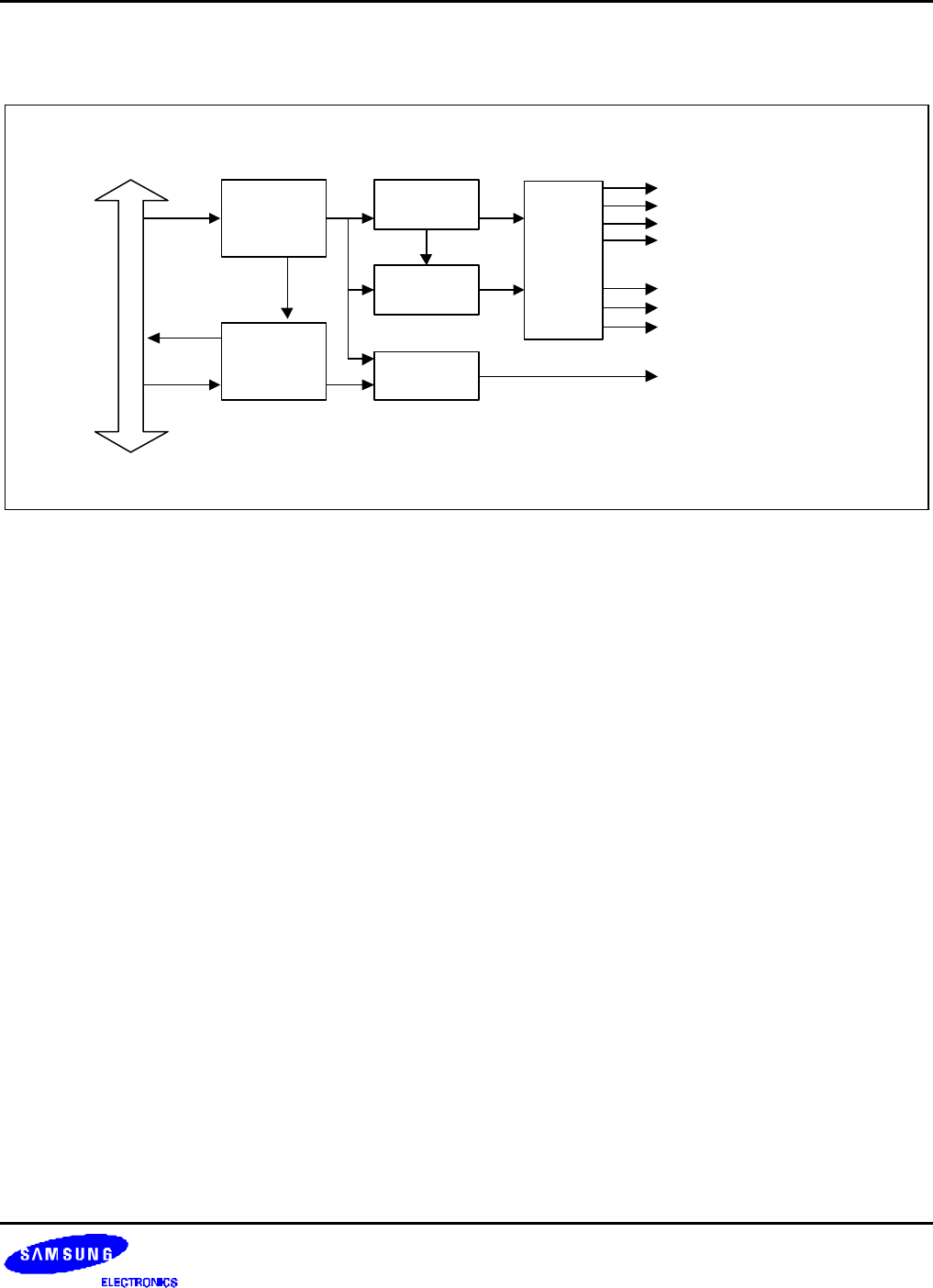

BLOCK DIAGRAM

System Bus

LPC3600 is a timing control logic unit for LTS350Q1-PD1 or LTS350Q1-PD2.

REGBANK

LCDCDMA

VIDPRCS

LPC3600

TIMEGEN

VD[23:0]

VCLK /LCD_HCLK

VLINE / HSYNC / CPV

VFRAME / VSYNC / STV

VM / VDEN / TP

LCDVF0

LCDVF1

LCDVF2

.

.

.

VIDEO

MUX

Figure 15-1. LCD Controller Block Diagram

The S3C2410A LCD controller is used to transfer the video data and to generate the necessary control signals, such

as VFRAME, VLINE, VCLK, VM, and so on. In addition to the control signals, the S3C2410A has the data ports for

video data, which are VD[23:0] as shown in Figure 15-1. The LCD controller consists of a REGBANK, LCDCDMA,

VIDPRCS, TIMEGEN, and LPC3600 (See the Figure 15-1 LCD Controller Block Diagram). The REGBANK has 17

programmable register sets and 256x16 palette memory which are used to configure the LCD controller. The

LCDCDMA is a dedicated DMA, which can transfer the video data in frame memory to LCD driver automatically. By

using this special DMA, the video data can be displayed on the screen without CPU intervention. The VIDPRCS

receives the video data from the LCDCDMA and sends the video data through the VD[23:0] data ports to the LCD

driver after changing them into a suitable data format, for example 4/8-bit single scan or 4-bit dual scan display

mode. The TIMEGEN consists of programmable logic to support the variable requirements of interface timing and

rates commonly found in different LCD drivers. The TIMEGEN block generates VFRAME, VLINE, VCLK, VM, and so

on.

The description of data flow is as follows:

FIFO memory is present in the LCDCDMA. When FIFO is empty or partially empty, the LCDCDMA requests data

fetching from the frame memory based on the burst memory transfer mode (consecutive memory fetching of 4 words

(16 bytes) per one burst request without allowing the bus mastership to another bus master during the bus transfer).

When the transfer request is accepted by bus arbitrator in the memory controller, there will be four successive word

data transfers from system memory to internal FIFO. The total size of FIFO is 28 words, which consists of 12 words

FIFOL and 16 words FIFOH, respectively. The S3C2410A has two FIFOs to support the dual scan display mode. In

case of single scan mode, one of the FIFOs (FIFOH) can only be used.