S3C2410A DMA

8-3

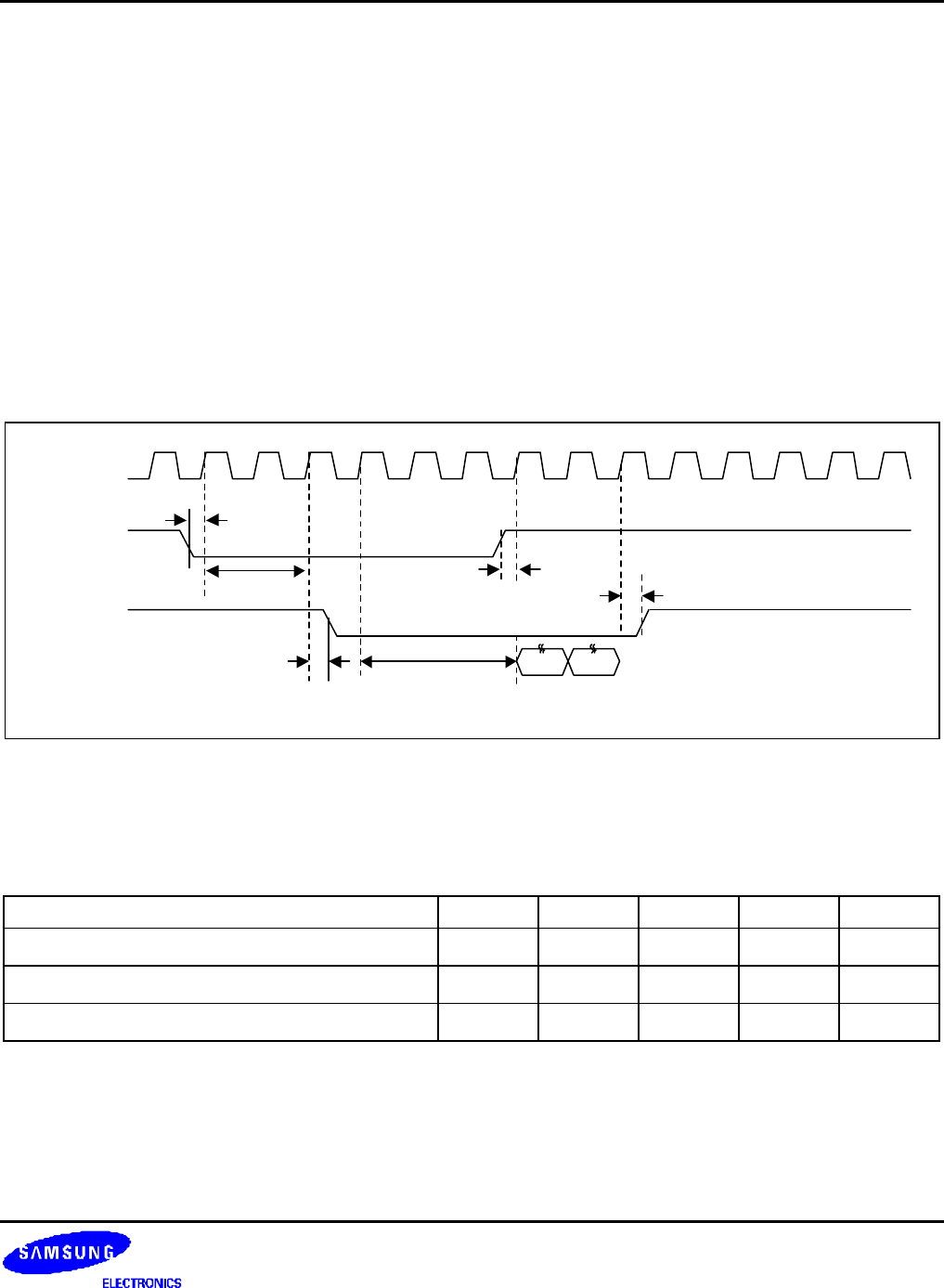

EXTERNAL DMA DREQ/DACK PROTOCOL

There are three types of external DMA request/acknowledge protocols (Single service Demand, Single service

Handshake and Whole service Handshake mode). Each type defines how the signals like DMA request and

acknowledge are related to these protocols.

Basic DMA Timing

The DMA service means performing paired Reads and Writes cycles during DMA operation, which can make one

DMA operation. Figure 8-1 shows the basic Timing in the DMA operation of the S3C2410A.

— The setup time and the delay time of XnXDREQ and XnXDACK are the same in all the modes.

— If the completion of XnXDREQ meets its setup time, it is synchronized twice and then XnXDACK is asserted.

— After assertion of XnXDACK, DMA requests the bus and if it gets the bus it performs its operations. XnXDACK is

deasserted when DMA operation is completed.

XSCLK

tXRS

tXRS

tCADL

tCADH

2 SCLK

XnXDREQ

XnXDACK

Read Write

Min. 3 SCLK

Figure 8-1. Basic DMA Timing Diagram

Table 8-2. DMA Controller Module Signal Timing Constants

(V

DD

= 1.8 V ± 0.15 V/2.0V ± 0.1V, T

A

= -40 to 85 °C, V

EXT

= 3.3V ± 0.3V)

Parameter Symbol Min Typ. Max Unit

eXternal Request Setup t

XRS

2 – 6 / 5 ns

aCcess to Ack Delay when Low transition t

CADL

9 – 11 / 10 ns

aCcess to Ack Delay when High transition t

CADH

9 – 11 / 10 ns