ARM920T PROCESSOR PROGRAMMER'S MODEL

2-21

REGISTER 10: TLB LOCK DOWN REGISTER

Register 10 is the TLB lock down register. The TLB lock down register is 0x0 on reset. There is a TLB lock down

register for each of the TLBs, the value of opcode_2 determines which TLB register to access:

opcode_2 = 0x0 causes the D TLB register to be accessed

opcode_2 = 0x1 causes the I TLB register to be accessed.

Reading CP15 register 10 returns the value of the TLB lock down counter base register, the current victim number

and the preserve bit (P bit). Note that bits [19:1] are unpredictable when read.

Writing CP15 register 10 updates the TLB lock down counter base register, the current victim pointer and the state of

the preserve bit. Bits [19:1] should be zero when written.

Table 2-19 shows the instructions needed to access the TLB lock down register.

Table 2-19. Accessing the TLB Lock Down Register 10

Function Data Instruction

Read D TLB lock down TLB lock-down MRC p15,0,Rd,c10,c0,0

Write D TLB lock down TLB lock-down MCR p15,0,Rd,c10,c0,0

Read I TLB lock down TLB lock-down MRC p15,0,Rd,c10,c0,1

Write I TLB lock down TLB lock-down MCR p15,0,Rd,c10,c0,1

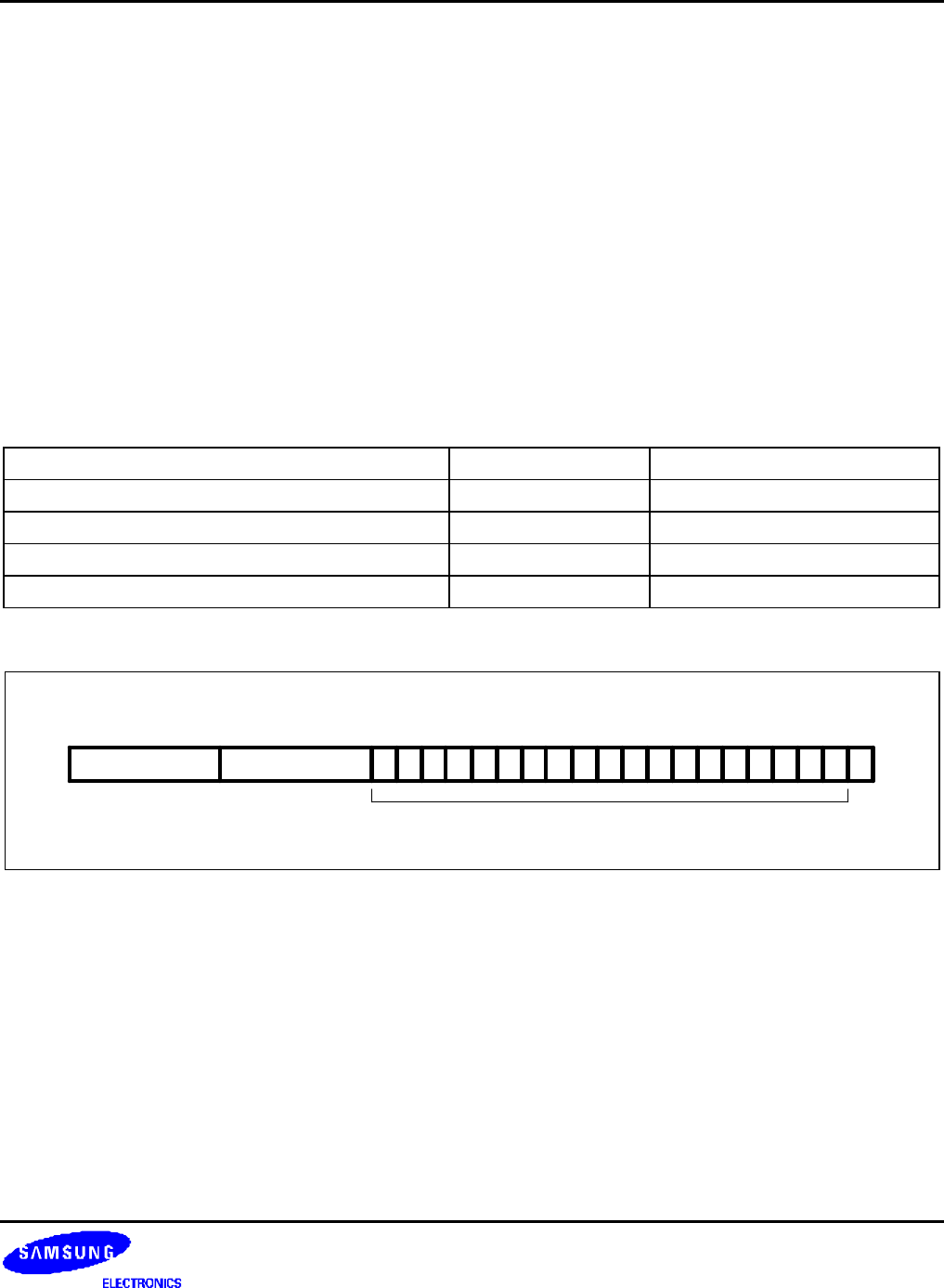

Figure 2-6 shows the format of bits in register 10.

31 19 1516 111220

0

8 7 4 3 0

0 0 0 0Base

26 25 10 9 5

0 0 0 P

2 1

00000000

13141718

UNP/SBZ

6

0 0 0Victim

Figure 2-6. Register 10

The entries in the TLBs are replaced using a round robin replacement policy. This is implemented using a victim

counter which counts from entry 0 up to 63 and then wraps back round to the base value and continues counting,

wrapping around to the base value from 63 each time.

There are two mechanisms available for ensuring entries are not removed from the TLB:

Locking an entry down prevents it from being selected for overwriting during a table walk, this is achieved by

programming the base value to which the victim counter reloads. For example, if the bottom 3 entries (0–2) are to be

locked down, the base counter should be programmed to 3.

An entry can also be preserved during an Invalidate All instruction. This is done by ensuring the P bit is set when the

entry is loaded into the TLB.