ARM920T PROCESSOR MMU

3-3

MMU PROGRAM ACCESSIBLE REGISTERS

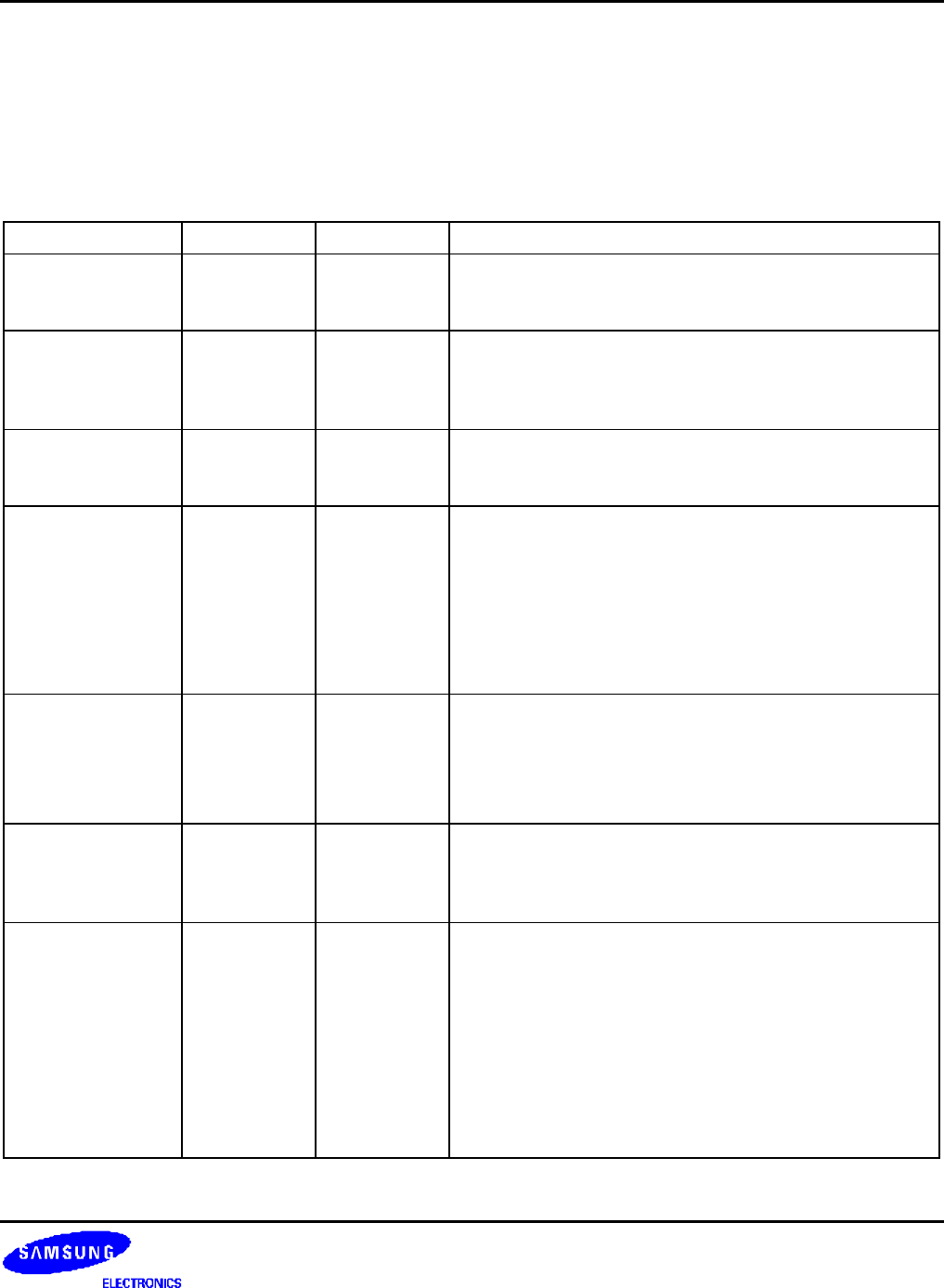

Table 3-1 shows system control coprocessor (CP15) registers which are used, in conjunction with page table

descriptors stored in memory, to determine the operation of the MMU

Table 3-1. CP15 Register Functions

Register Number Bits Register description

Control register 1 M, A, S, R Contains bits to enable the MMU (M bit), enable data

address alignment checks (A bit) and to control the

access protection scheme (S bit and R bit).

Translation table

base register

2 31:14 Holds the physical address of the base of the translation

table maintained in main memory.

This base address must be on a 16KB boundary and is

common to both TLBs.

Domain access

control register

3 31:0 Comprises sixteen 2-bit fields.

Each field defines the access control attributes for one of

16 domains (D15–D0).

Fault status register 5 (I & D) 7:0 Indicates the cause of a data and prefetch abort and the

domain number of the aborted access, when an abort

occurs.

Bits 7:4 specify which of the 16 domains (D15–D0) was

being accessed when a fault occurred.

Bits 3:0 indicate the type of access being attempted.

The value of all other bits is unpredictable. The encoding of

these bits is shown in Table 3-4 on page 3-18 .

Fault address

register

6 (D) 31:0 Holds the virtual address associated with the access that

caused the data abort. See Table 3-4 on page 3-18 for

details of the address stored for each type of fault.

ARM9TDMI Register 14 can be used to determine the

virtual address associated with a prefetch abort.

TLB operations

register

8 31:0 Writing to this register causes the MMU to perform TLB

maintenance operations; either invalidating all the

(unpreserved) entries in the TLB, or invalidating a specific

entry.

TLB lock down

register

10 (I & D) 31:20 & 0 Allows specific page table entries to be locked into the

TLB and the TLB victim index to be read/written:

opcode 2 = 0x0 accesses the D TLB lock down register

opcode 2 = 0x1 accesses the I TLB lock down register.

Locking entries in the TLB guarantees that accesses to

the locked page or section can proceed without incurring

the time penalty of a TLB miss. This allows the execution

latency for time-critical pieces of code such as interrupt

handlers to be minimized.