PROGRAMMER'S MODEL ARM920T PROCESSOR

2-8

REGISTER 0: CACHE TYPE REGISTER

This is a read-only register which contains information about the size and architecture of the caches, allowing

operating systems to establish how to perform such operations as cache cleaning and lockdown. Future ARM

cached processors will contain this register, allowing RTOS vendors to produce future-proof versions of their

operating systems.

The cache type register is accessed by reading CP15 register 0 with the opcode_2 field set to 1. For example:

MRC p15,0,Rd,c0,c0,1; returns cache details

The format of the register is shown in Table 2-6.

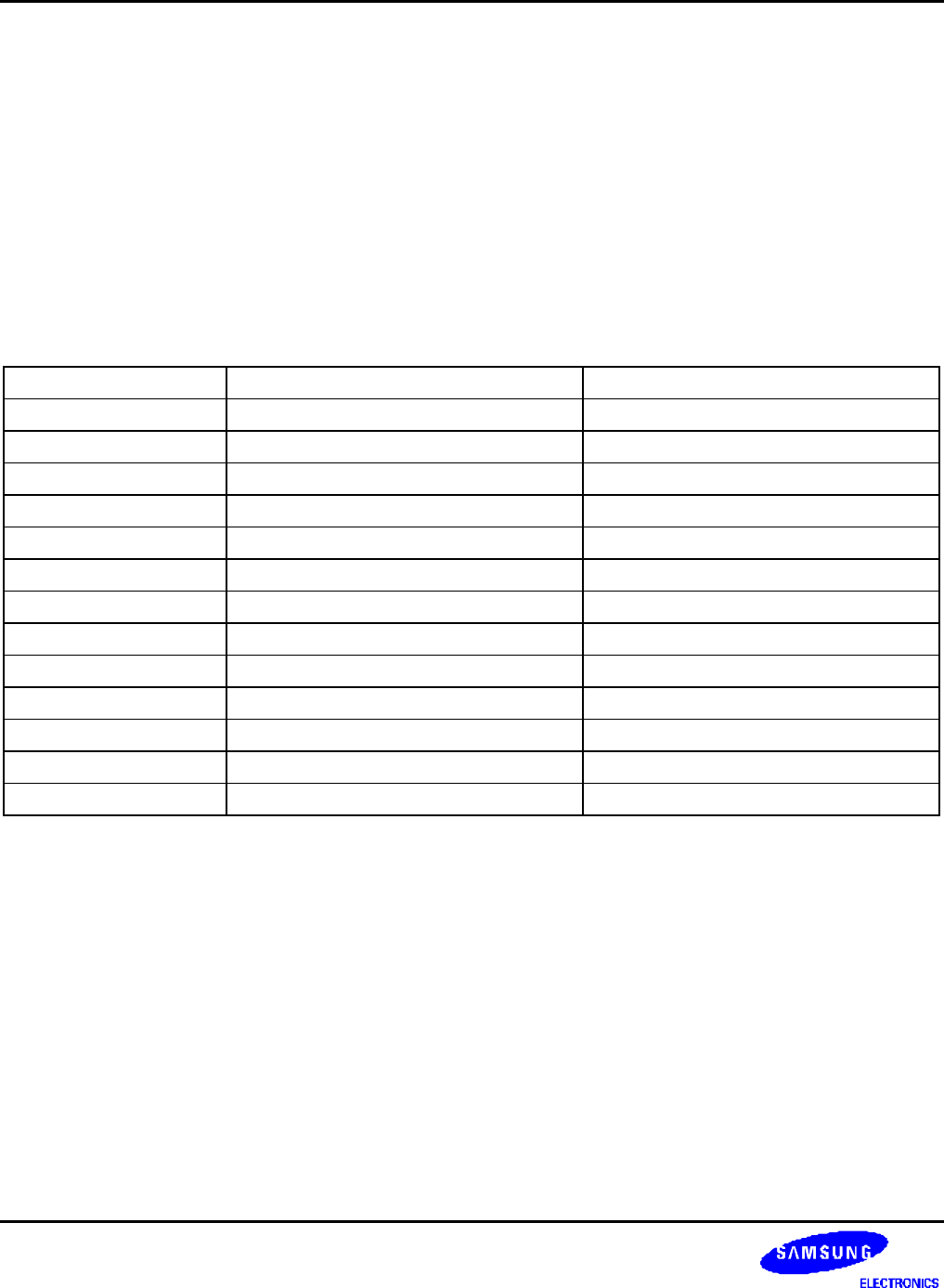

Table 2-6. Cache Type Register Format

Register Bits Function Value

31:29 Reserved 000

28:25 Cache type 0110

24 Harvard/Unified 1 (defines Harvard cache)

23:21 Reserved 000

20:18 DCache size 101 (defines 16KB)

17:15 DCache associativity 110 (defines 64 way)

14 Reserved 0

13:12 DCache words per line 10 (defines 8 words per line)

11:9 Reserved 000

8:6 ICache size 101 (defines 16KB)

5:3 ICache Associativity 110 (defines 64 way)

2 Reserved 0

1:0 ICache words per line 10 (defines 8 words per line)

Bits [28:25] indicate which major cache class the implementation falls into. 0x6 means that the cache provides:

• Cache-clean-step operation

• Cache-flush-step operation

• Lock down facilities