S3C2410A MICROPROCESSOR xxix

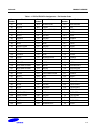

List of Table (Concluded)

Figure Title Page

Number Number

2-1 ARM9TDMI Implementation Option........................................................................2-2

2-2 CP15 Register Map .............................................................................................2-4

2-3 CP15 Abbreviations .............................................................................................2-5

2-4 Address Types in ARM920...................................................................................2-6

2-5 Register 0: ID Code .............................................................................................2-7

2-6 Cache Type Register Format ................................................................................2-8

2-7 Cache Size Encoding ..........................................................................................2-9

2-8 Cache associativity encoding................................................................................2-9

2-9 Line Length Encoding ..........................................................................................2-10

2-10 Control Register 1-bit Functions............................................................................2-11

2-11 Clocking Modes ..................................................................................................2-11

2-12 Register 2: Translation Table Base........................................................................2-12

2-13 Register 3: Domain Access Control.......................................................................2-13

2-14 Fault Status Register...........................................................................................2-14

2-15 Function Descriptions Register 7..........................................................................2-15

2-16 Cache Operations Register 7................................................................................2-16

2-17 TLB Operations Register 8...................................................................................2-18

2-18 Accessing the Cache Lock Down Register 9..........................................................2-20

2-19 Accessing the TLB Lock Down Register 10............................................................2-21

3-1 CP15 Register Functions .....................................................................................3-3

3-2 Interpreting Level One Descriptor Bits [1:0] ............................................................3-8

3-3 Interpreting Page Table Entry Bits 1:0...................................................................3-11

3-4 Priority Encoding of Fault Status...........................................................................3-18

3-5 Interpreting Access Control Bits in Domain Access Control Register........................3-19

3-6 Interpreting Access Permission (AP) Bits..............................................................3-20

4-1 Data Cache and Write Buffer Configuration.............................................................4-7

5-1 ARM920T Clocking..............................................................................................5-1

5-2 Synchronous Clocking Mode................................................................................5-2

5-3 Switching from FCLK to BCLK in Synchronous Mode .............................................5-2

5-4 Asynchronous Clocking Mode ..............................................................................5-3

5-5 Switching from FCLK to BCLK in Asynchronous Mode............................................5-3