THUMB INSTRUCTION SET S3C2410A

4-24

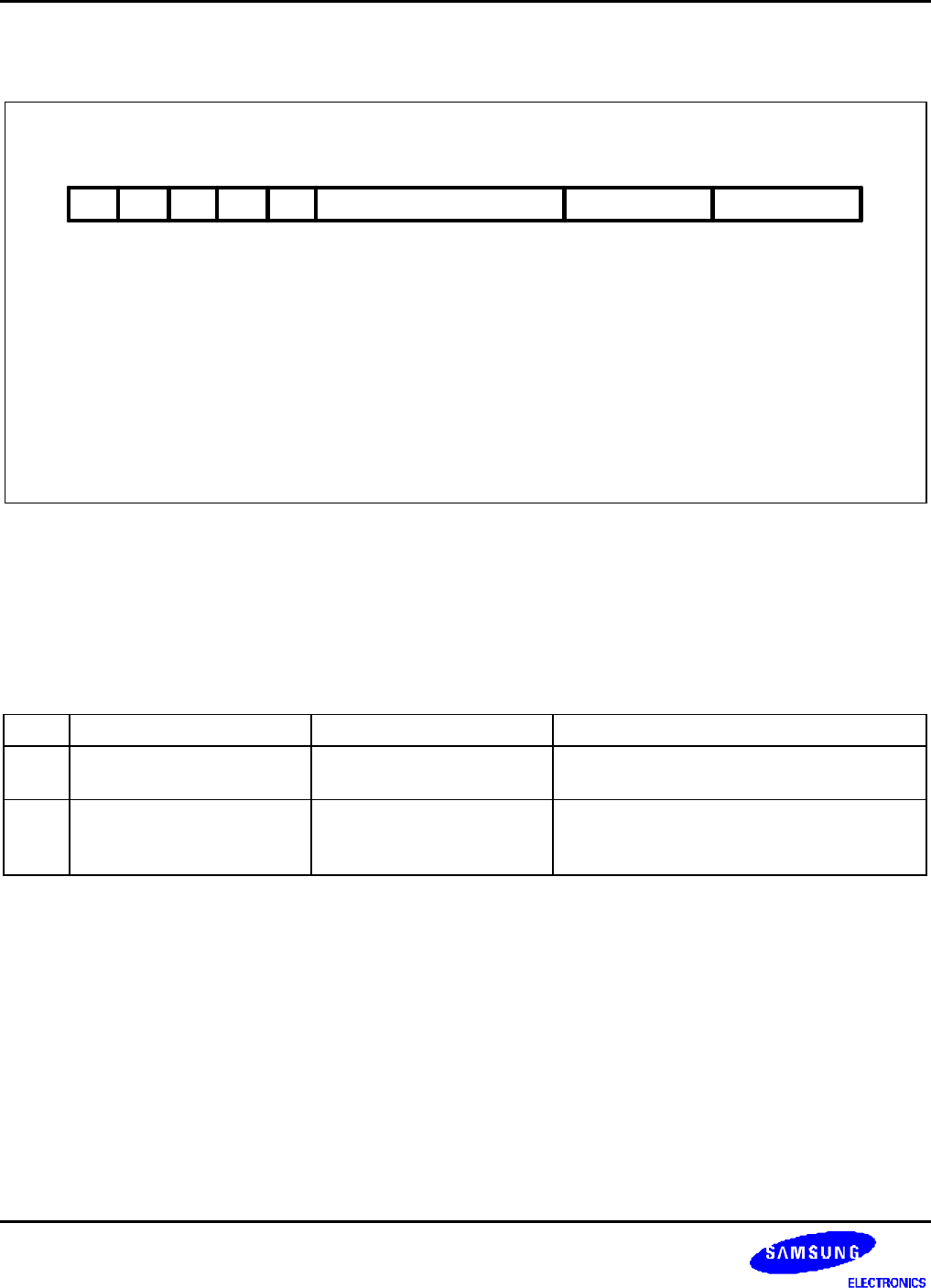

FORMAT 10: LOAD/STORE HALFWORD

[2:0] Source/Destination Register

[5:3] Base Register

[10:6] Immediate Value

[11] Load/Store Flag

0 = Store to memory

1 = Load from memory

15 0

0

14

10

6 5

3 2

Rd1 0

13 12

11

Rb0 L Offset5

Figure 4-11. Format 10

OPERATION

These instructions transfer halfword values between a Lo register and memory. Addresses are pre-indexed, using a

6-bit immediate value. The THUMB assembler syntax is shown in Table 4-11.

Table 4-11. Halfword Data Transfer Instructions

L THUMB assembler ARM equivalent Action

0 STRH Rd, [Rb, #Imm] STRH Rd, [Rb, #Imm] Add #Imm to base address in Rb and store

bits 0 - 15 of Rd at the resulting address.

1 LDRH Rd, [Rb, #Imm] LDRH Rd, [Rb, #Imm] Add #Imm to base address in Rb. Load bits

0-15 from the resulting address into Rd and

set bits 16-31 to zero.

NOTE: #Imm is a full 6-bit address but must be halfword-aligned (ie with bit 0 set to 0) since the assembler places

#Imm >> 1 in the Offset5 field.