S3C2410A ARM INSTRUCTION SET

3-5

BRANCH AND EXCHANGE (BX)

This instruction is only executed if the condition is true. The various conditions are defined in Table 3-2.

This instruction performs a branch by copying the contents of a general register, Rn, into the program counter, PC.

The branch causes a pipeline flush and refill from the address specified by Rn. This instruction also permits the

instruction set to be exchanged. When the instruction is executed, the value of Rn[0] determines whether the

instruction stream will be decoded as ARM or THUMB instructions.

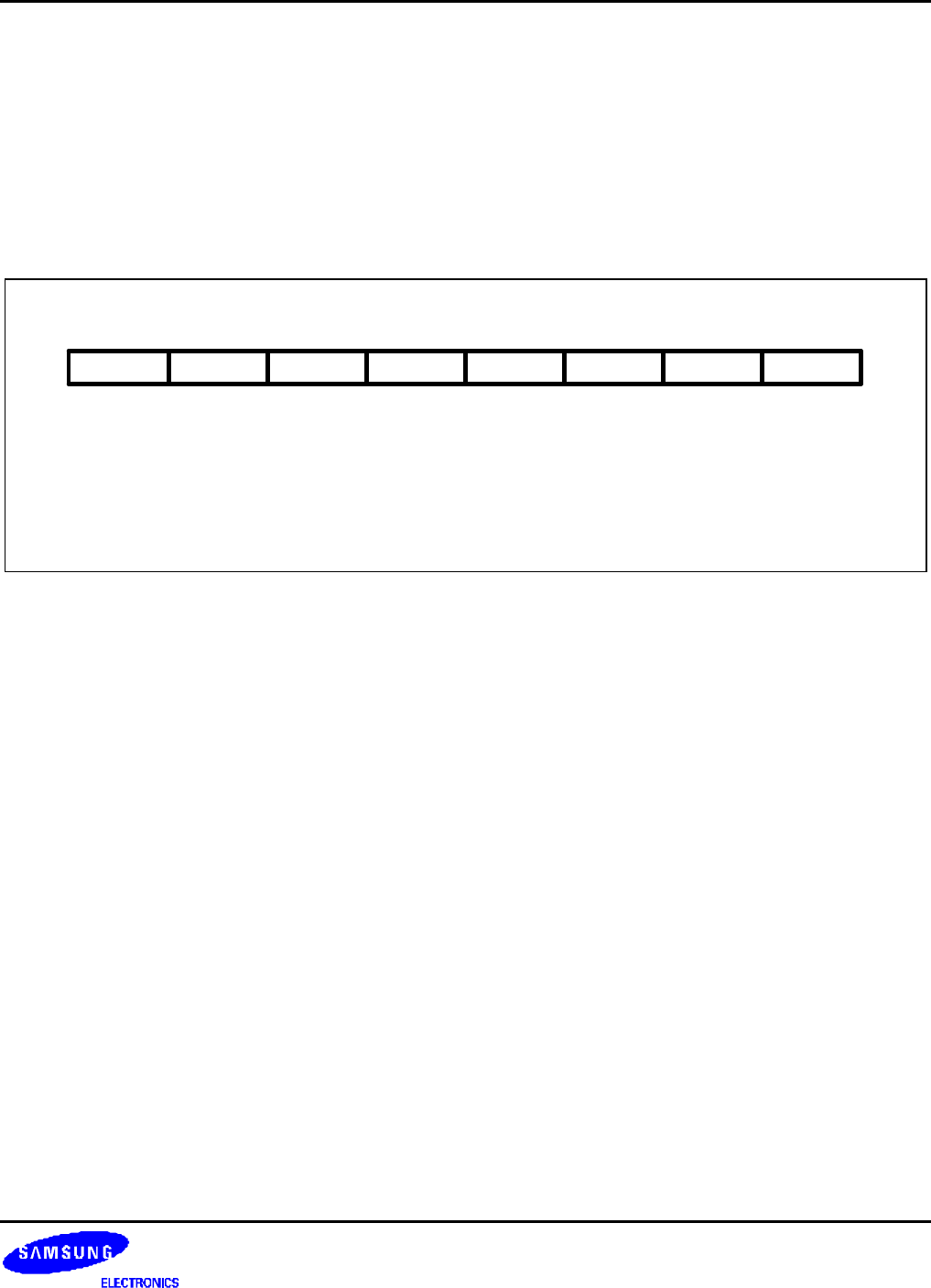

31 2427 19 15 8 7 0

00 0 1 10 0 0 11 1 1 11 1 1 11 1 1 00 0 1Cond Rn

28 16 111223 20 4 3

[3:0] Operand Register

If bit0 of Rn = 1, subsequent instructions decoded as THUMB instructions

If bit0 of Rn =0, subsequent instructions decoded as ARM instructions

[31:28] Condition Field

Figure 3-2. Branch and Exchange Instructions

INSTRUCTION CYCLE TIMES

The BX instruction takes 2S + 1N cycles to execute, where S and N are defined as sequential (S-cycle) and non-

sequential (N-cycle), respectively.

ASSEMBLER SYNTAX

BX - branch and exchange.

BX {cond} Rn

{cond} Two character condition mnemonic. See Table 3-2.

Rn is an expression evaluating to a valid register number.

USING R15 AS AN OPERAND

If R15 is used as an operand, the behavior is undefined.