S3C2410A USB DEVICE

13-17

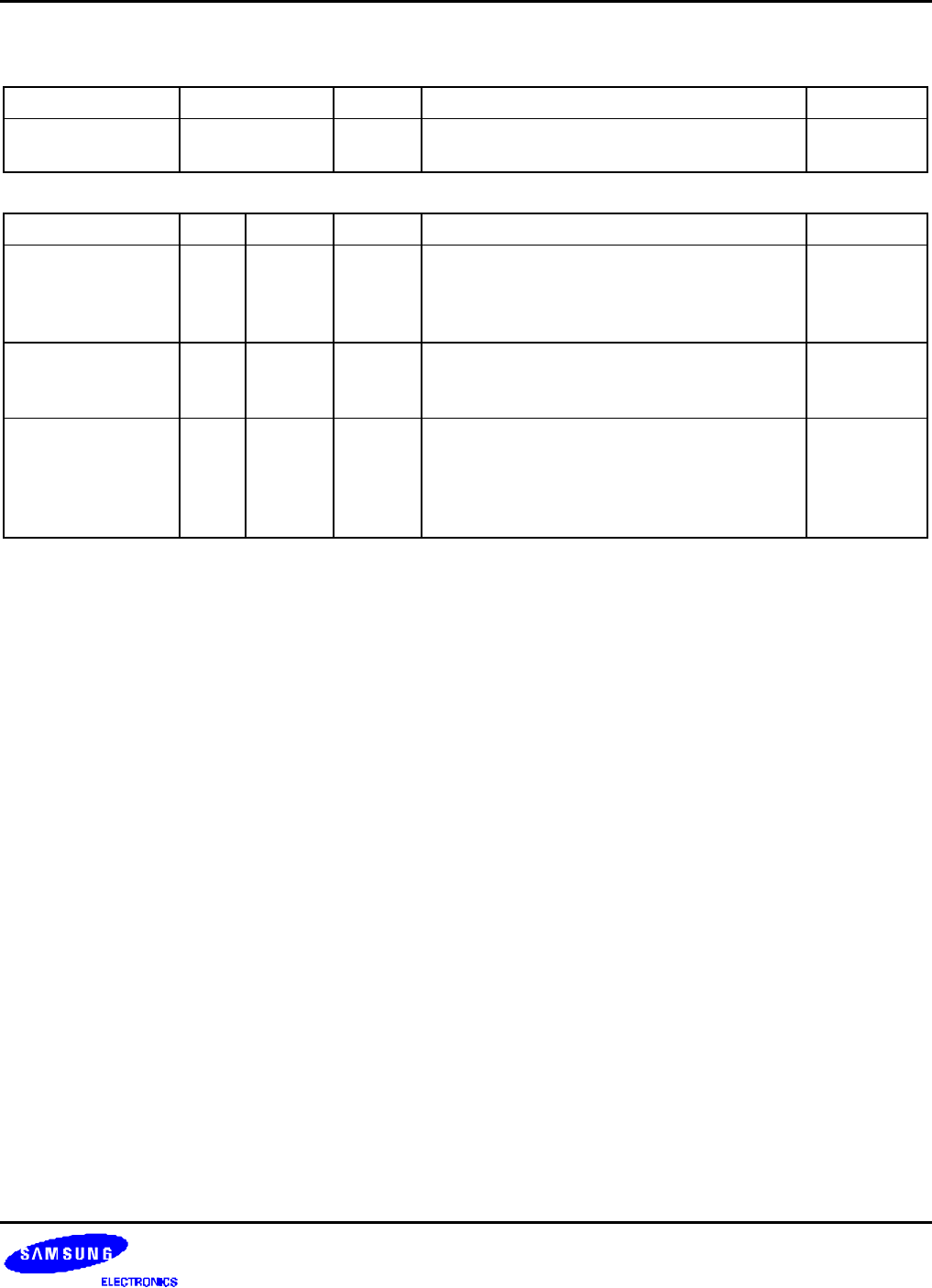

END POINT OUT CONTROL STATUS REGISTER (OUT_CSR1_REG/OUT_CSR2_REG) (Continued)

Register Address R/W Description Reset Value

OUT_CSR2_REG 0x52000194(L)

0x52000197(B)

R/W

(byte)

End Point out control status register2 0x00

OUT_CSR2_REG Bit MCU USB Description Initial State

AUTO_CLR [7] R/W R If the MCU is set, whenever the MCU reads

data from the OUT FIFO, OUT_PKT_RDY will

automatically be cleared by the logic without

any intervention from the MCU.

0

ISO [6] R/W R Determine endpoint transfer type.

0: Configures endpoint to Bulk mode.

1: Reserved

0

OUT_DMA_INT_

MASK

[5] R/W R Determine whether the interrupt should be

issued or not.

OUT_PKT_RDY condition happens. This is

only useful for DMA mode

0 = Interrupt Enable 1 = Interrupt Disable

0