PRODUCT OVERVIEW S3C2410A

1-28

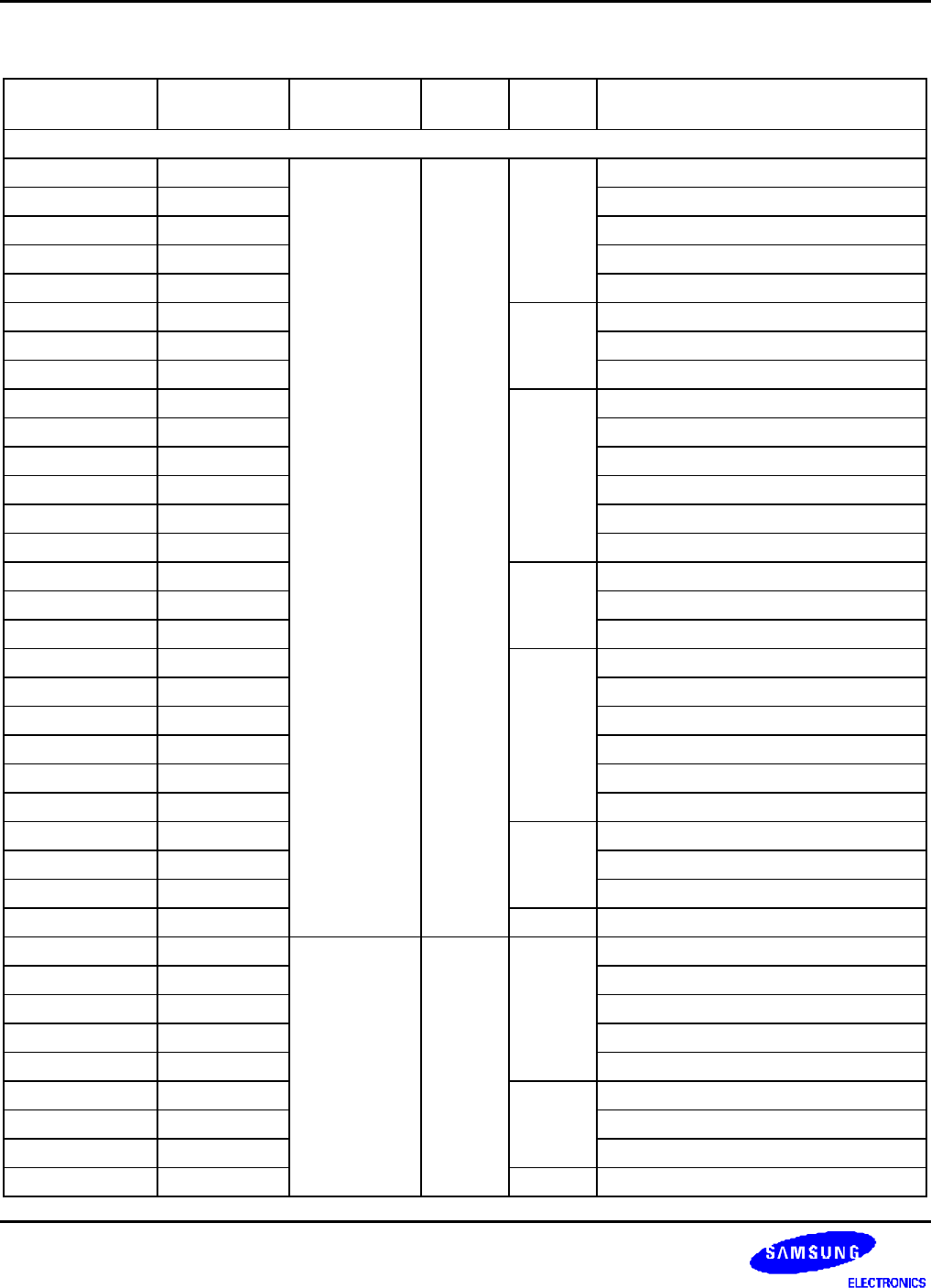

Table 1-4. S3C2410A Special Registers (Continued)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

DMA

DISRC0 0x4B000000 ← W R/W DMA 0 Initial Source

DISRCC0 0x4B000004 DMA 0 Initial Source Control

DIDST0 0x4B000008 DMA 0 Initial Destination

DIDSTC0 0x4B00000C DMA 0 Initial Destination Control

DCON0 0x4B000010 DMA 0 Control

DSTAT0 0x4B000014 R DMA 0 Count

DCSRC0 0x4B000018 DMA 0 Current Source

DCDST0 0x4B00001C DMA 0 Current Destination

DMASKTRIG0 0x4B000020 ← W R/W DMA 0 Mask Trigger

DISRC1 0x4B000040 DMA 1 Initial Source

DISRCC1 0x4B000044 DMA 1 Initial Source Control

DIDST1 0x4B000048 DMA 1 Initial Destination

DIDSTC1 0x4B00004C DMA 1 Initial Destination Control

DCON1 0x4B000050 DMA 1 Control

DSTAT1 0x4B000054 R DMA 1 Count

DCSRC1 0x4B000058 DMA 1 Current Source

DCDST1 0x4B00005C ← W DMA 1 Current Destination

DMASKTRIG1 0x4B000060 R/W DMA 1 Mask Trigger

DISRC2 0x4B000080 DMA 2 Initial Source

DISRCC2 0x4B000084 DMA 2 Initial Source Control

DIDST2 0x4B000088 DMA 2 Initial Destination

DIDSTC2 0x4B00008C DMA 2 Initial Destination Control

DCON2 0x4B000090 DMA 2 Control

DSTAT2 0x4B000094 R DMA 2 Count

DCSRC2 0x4B000098 ← W DMA 2 Current Source

DCDST2 0x4B00009C DMA 2 Current Destination

DMASKTRIG2 0x4B0000A0 R/W DMA 2 Mask Trigger

DISRC3 0x4B0000C0 ← W R/W DMA 3 Initial Source

DISRCC3 0x4B0000C4 DMA 3 Initial Source Control

DIDST3 0x4B0000C8 DMA 3 Initial Destination

DIDSTC3 0x4B0000CC DMA 3 Initial Destination Control

DCON3 0x4B0000D0 DMA 3 Control

DSTAT3 0x4B0000D4 R DMA 3 Count

DCSRC3 0x4B0000D8 DMA 3 Current Source

DCDST3 0x4B0000DC DMA 3 Current Destination

DMASKTRIG3 0x4B0000E0 R/W DMA 3 Mask Trigger