IIC-BUS INTERFACE S3C2410A

20-12

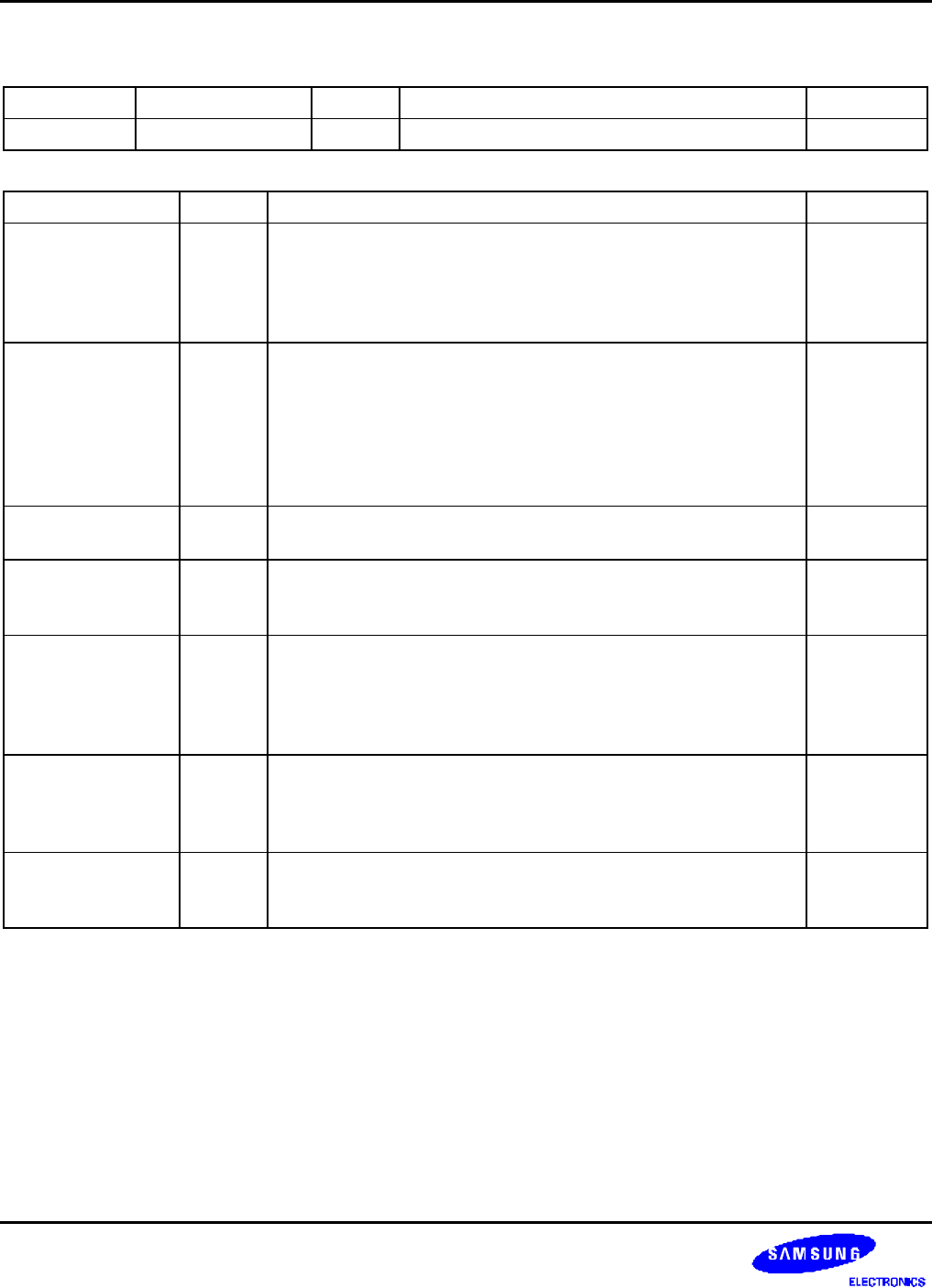

MULTI-MASTER IIC-BUS CONTROL/STATUS (IICSTAT) REGISTER

Register Address R/W Description Reset Value

IICSTAT 0x54000004 R/W IIC-Bus control/status register 0x0

IICSTAT Bit Description Initial State

Mode selection [7:6] IIC-bus master/slave Tx/Rx mode select bits.

00: Slave receive mode

01: Slave transmit mode

10: Master receive mode

11: Master transmit mode

00

Busy signal status /

START STOP

condition

[5] IIC-Bus busy signal status bit.

0 = read) Not busy (when read)

write) STOP signal generation

1 = read) Busy (when read)

write) START signal generation.

The data in IICDS will be transferred

automatically just after the start signal.

0

Serial output [4] IIC-bus data output enable/disable bit.

0 = Disable Rx/Tx, 1 = Enable Rx/Tx

0

Arbitration status

flag

[3] IIC-bus arbitration procedure status flag bit.

0 = Bus arbitration successful

1 = Bus arbitration failed during serial I/O

0

Address-as-slave

status flag

[2] IIC-bus address-as-slave status flag bit.

0 = Cleared when START/STOP condition was

detected

1 = Received slave address matches the address

value in the IICADD

0

Address zero status

flag

[1] IIC-bus address zero status flag bit.

0 = Cleared when START/STOP condition was

detected.

1 = Received slave address is 00000000b.

0

Last-received bit

status flag

[0] IIC-bus last-received bit status flag bit.

0 = Last-received bit is 0 (ACK was received).

1 = Last-received bit is 1 (ACK was not received).

0