ARM920T PROCESSOR PROGRAMMER'S MODEL

2-23

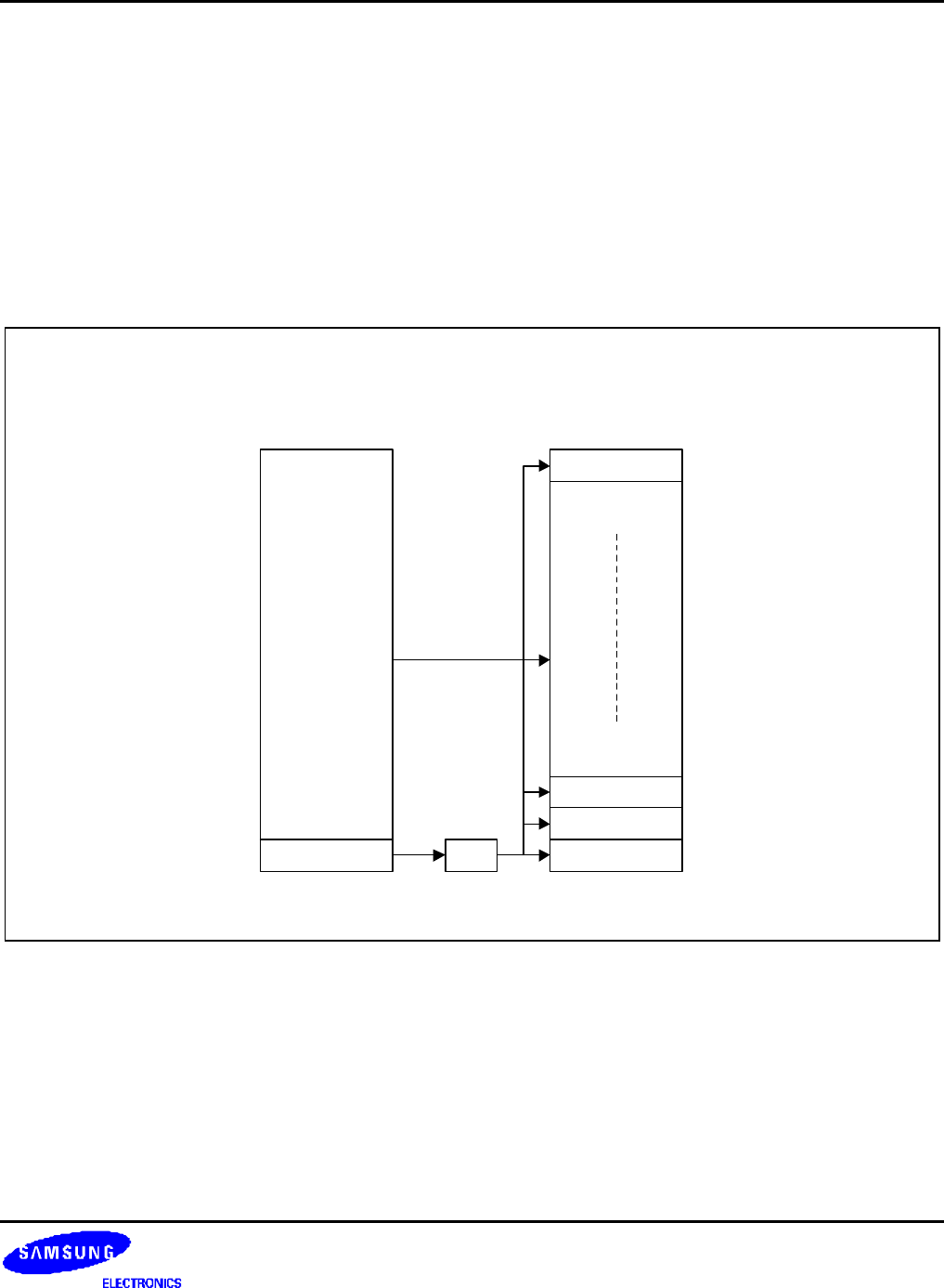

Using the process Identifier (ProcID)

Addresses issued by the ARM9TDMI core in the range 0 to 32MB are translated by CP15 register 13, the ProcID

register. Address A becomes A + (ProcID x 32MB). It is this translated address that is seen by both the Caches and

MMU. Addresses above 32MB undergo no translation. This is shown in Figure 2-8 on page 2-23 .

The ProcID is a seven bit field, enabling 64 x 32MB processes to be mapped.

NOTE

If ProcID is zero, as it is on reset, then there is a flat mapping between the ARM9TDMI and the Caches and

MMU.

Virtual address (VA)

issued by ARM9TDMI

Modified virtual address (MVA)

input to caches and MMU

63

0

1

2

C13

4GB

32MB

0

4GB

32MB

0

64MB

Figure 2-8. Address Mapping Using CP15 Register 13