S3C2410A SPI INTERFACE

22-1

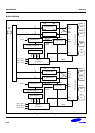

22 SPI INTERFACE

OVERVIEW

The S3C2410A Serial Peripheral Interface (SPI) can interface the serial data transfer. The S3C2410A includes two

SPI, each of which has two 8-bit shift registers for transmission and receiving, respectively. During an SPI transfer,

data is simultaneously transmitted (shifted out serially) and received (shifted in serially). 8-bit serial data at a

frequency is determined by its corresponding control register settings. If you only want to transmit, received data can

be dummy. Otherwise, if you only want to receive, you should transmit dummy '1' data.

There are 4 I/O pin signals associated with SPI transfers: the SCK (SPICLK0,1), the MISO (SPIMISO0,1) data line,

the MOSI (SPIMOSI0,1) data line, and the active low /SS (nSS0,1) pin (input).

FEATURES

— SPI Protocol (ver. 2.11) compatible

— 8-bit Shift Register for transmit

— 8-bit Shift Register for receive

— 8-bit Prescaler logic

— Polling, Interrupt, and DMA transfer mode